Maxim Integrated DS33R11 User Manual

Page 204

DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

204 of 344

Register Name:

TR.T1RCR1

Register Description:

T1 Receive Control Register 1

Register Address:

03h

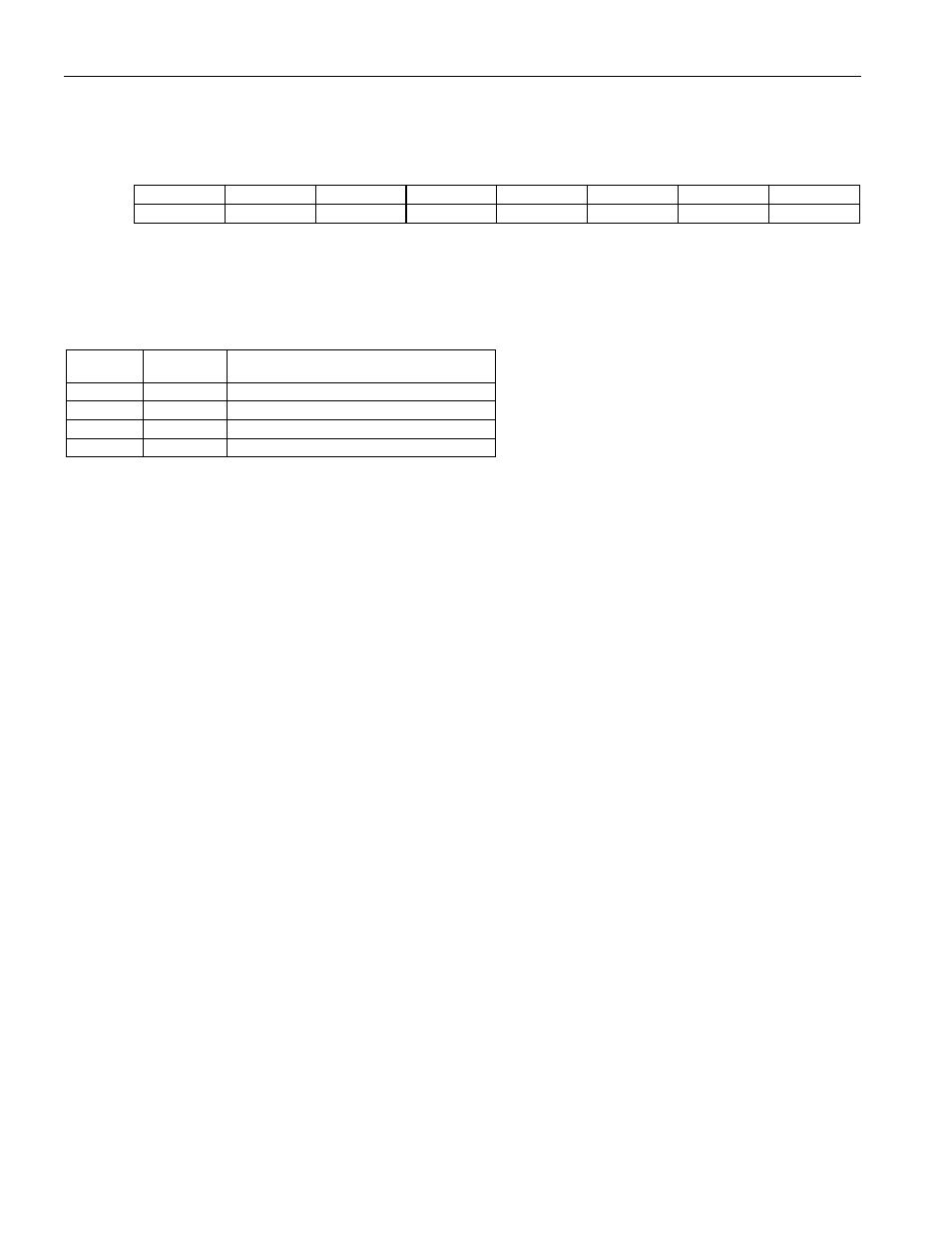

Bit

# 7 6 5 4 3 2 1 0

Name — ARC

OOF1

OOF2

SYNCC

SYNCT

SYNCE

RESYNC

Default

0 0 0 0 0 0 0 0

Bit 6: Auto Resync Criteria (ARC)

0 = resync on OOF or RCL event

1 = resync on OOF only

Bits 4- 5: Out-of-Frame Select Bits (OOF2, OOF1)

OOF2 OOF1

Out-Of-Frame

Criteria

0

0

2/4 frame bits in error

0

1

2/5 frame bits in error

1

0

2/6 frame bits in error

1

1

2/6 frame bits in error

Bit 3: Sync Criteria (SYNCC)

In D4 Framing Mode:

0 = search for Ft pattern, then search for Fs pattern

1 = cross couple Ft and Fs pattern

In ESF Framing Mode:

0 = search for FPS pattern only

1 = search for FPS and verify with CRC6

Bit 2: Sync Time (SYNCT)

0 = qualify 10 bits

1 = qualify 24 bits

Bit 1: Sync Enable (SYNCE)

0 = auto resync enabled

1 = auto resync disabled

Bit 0: Resynchronize (RESYNC) When toggled from low to high, a resynchronization of the receive-side framer

is initiated. Must be cleared and set again for a subsequent resync.