Gl.c1qpr, Gl.bisten – Maxim Integrated DS33R11 User Manual

Page 140

DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

140 of 344

Register Name:

GL.C1QPR

Register Description:

Connection 1 Queue Pointer Reset

Register Address:

12h

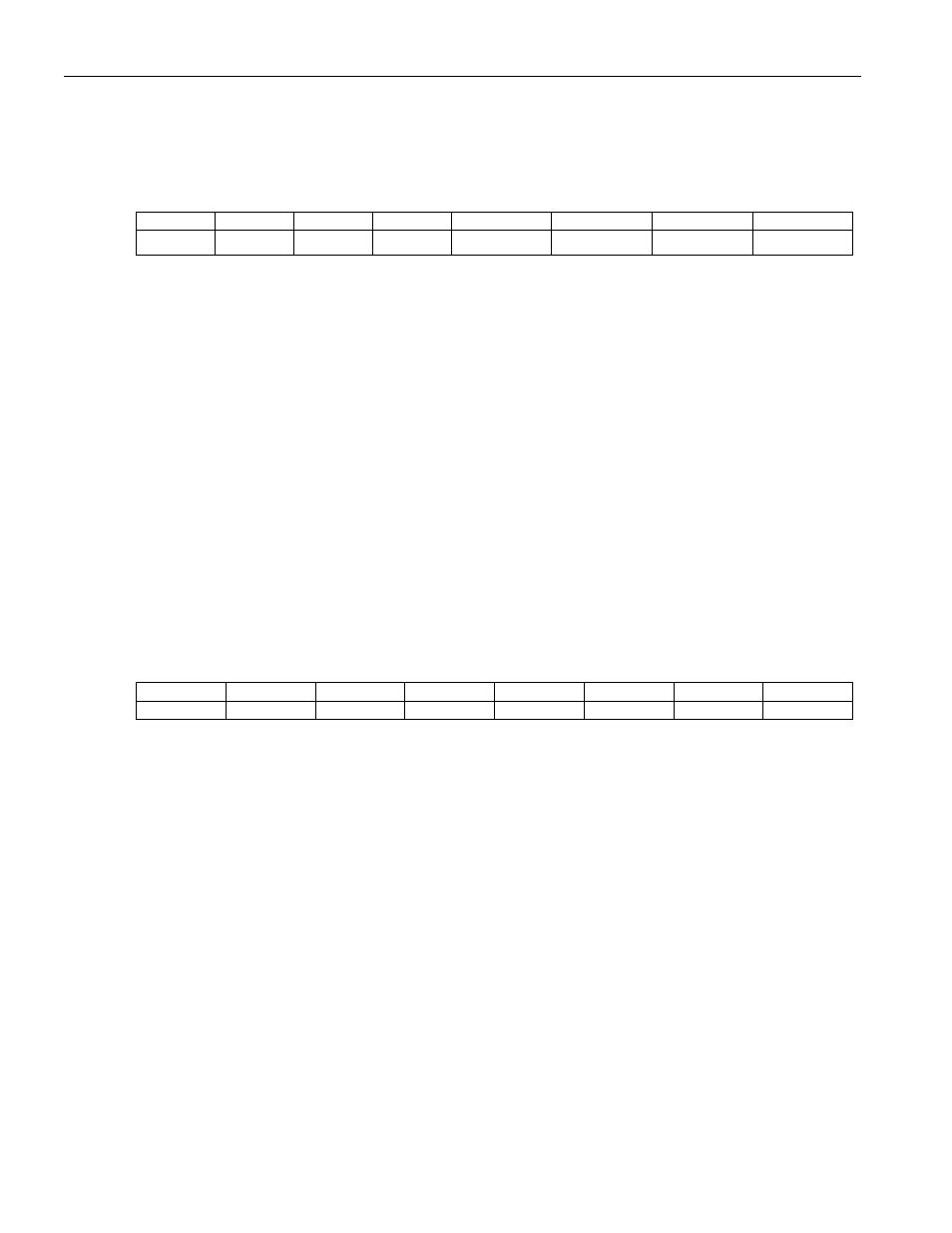

Bit

# 7 6 5 4 3

2

1

0

Name - - - -

C1MRPR

C1HWPR

C1MHPR

C1HRPR

Default

0 0 0 0 0

0

0

0

Bit 3: MAC Read Pointer Reset (C1MRPR) Setting this bit to 1 resets the receive queue read pointer for

connection 1. This queue pointer must be reset after a disconnect and before a connection. The user must clear

the bit before subsequent reset operations.

Bit 2: HDLC Write Pointer Reset (C1HWPR) Setting this bit to 1 resets the receive queue write pointer for

connection 1. This queue pointer must be reset after a disconnect and before a connection. The user must clear

the bit before subsequent reset operations.

Bit 1: HDLC Read Pointer Reset (C1MHPR) Setting this bit to 1 resets the transmit queue read pointer for

connection 1. This queue pointer must be reset after a disconnect and before a connection. The user must clear

the bit before subsequent reset operations.

Bit 0: MAC Transmit Write Pointer Reset (C1HRPR) Setting this bit to 1 resets the transmit queue write pointer

for connection 1. This queue pointer must be reset after a disconnect and before a connection. The user must clear

the bit before subsequent reset operations.

Register Name:

GL.BISTEN

Register Description:

BIST Enable

Register Address:

20h

Bit

# 7 6 5 4 3 2 1 0

Name

- - - - - - -

BISTE

Default

0 0 0 0 0 0 0 0

Bit 0: BIST Enable (BISTE) If this bit is set the DS33R11 performs BIST test on the SDRAM. Normal data

communication is halted while BIST enable is high. The user must reset the DS33R11 after completion of BIST test

before normal dataflow can begin.