Altera Nios Development Board User Manual

Page 41

Altera Corporation

A–3

September 2004

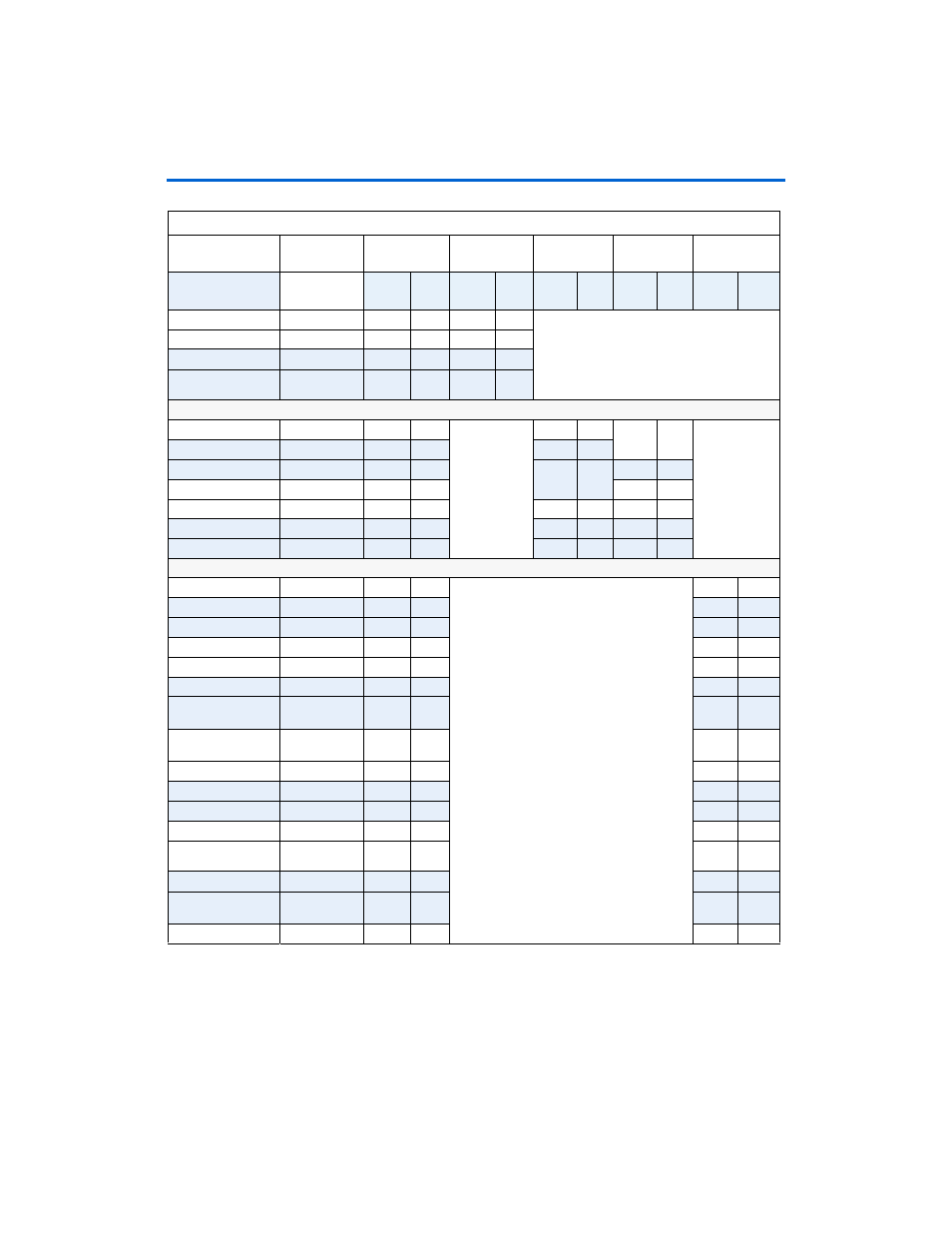

Pin

Name

Pin #

Pin

Name

Pin #

Pin

Name

Pin

#

Pin

Name

Pin #

Pin

Name

Pin #

FLASH_CS_n

Chip Select

IO

K19

CE_n

28

FLASH_OE-N

Read Enable

IO

F19

OE_n

30

FLASH_RW-N

Write Enable

IO

G19

WE_n

11

FLASH_RY-BY_N

Ready/Busy

IO

L18

RY/BY

_n

14

SRAM_BE_N0

Byte Enable 0

IO

M18

BE0#

39

SRAM_BE_N1

Byte Enable 1

IO

F17

BE1#

40

SRAM_BE_N2

Byte Enable 2

IO

J18

BE2#

39

SRAM_BE_N3

Byte Enable 3

IO

L17

BE3#

40

SRAM_CS_N

Chip Select

IO

B24

CS_n

6

CS_n

6

SRAM_OE_N

Read Enable

IO

B26

OE_n

41

OE_n

41

SRAM_WE_N

Write Enable

IO

C24

WE_n

17

WE_n

17

ENET_ADS_N

Address Strobe

IO

V25

ADS#

37

ENET_AEN

Address Enable

IO

V28

AEN

41

ENET_BE_N0

Byte Enable 0

IO

T22

BE0#

94

ENET_BE_N1

Byte Enable 1

IO

U26

BE1#

95

ENET_BE_N2

Byte Enable 2

IO

U25

BE2#

96

ENET_BE_N3

Byte Enable 3

IO

T19

BE3#

97

ENET_CYCLE_N

Bus Cycle

IO

U27

CYCLE

#

35

ENET_DATACS_N

Data Chip

Select

IO

T20

DATA

CS#

34

ENET_INTRQ0

Interrupt

IO

V27

INTRO

29

ENET_IOCHRDY

IO Char Ready

IO

V26

ARDY

38

ENET_IOR_N

Read

IO

T23

RD#

31

ENET_IOW_N

Write

IO

T24

WR#

32

ENET_LCLK

Local Bus

Clock

IO

R26

LCLK

42

ENET_LDEV_N

Local Device

IO

T26

LDEV#

45

ENET_RDYRTN_N

Ready Return

IO

T28

RDYR

TN#

46

ENET_W_R_N

Write/Read

IO

T21

W/R#

36

Table A–9. Shared Bus Table (Part 3 of 3)

NET Name

NET

Description

PLD (U53)

Flash (U5)

SRAM (U35) SRAM (U36) Ethernet (U4)