Block diagram, Default reference design – Altera Nios Development Board User Manual

Page 10

1–2

Altera

Corporation

Nios Development Board Reference Manual, Stratix Edition

September 2004

General Description

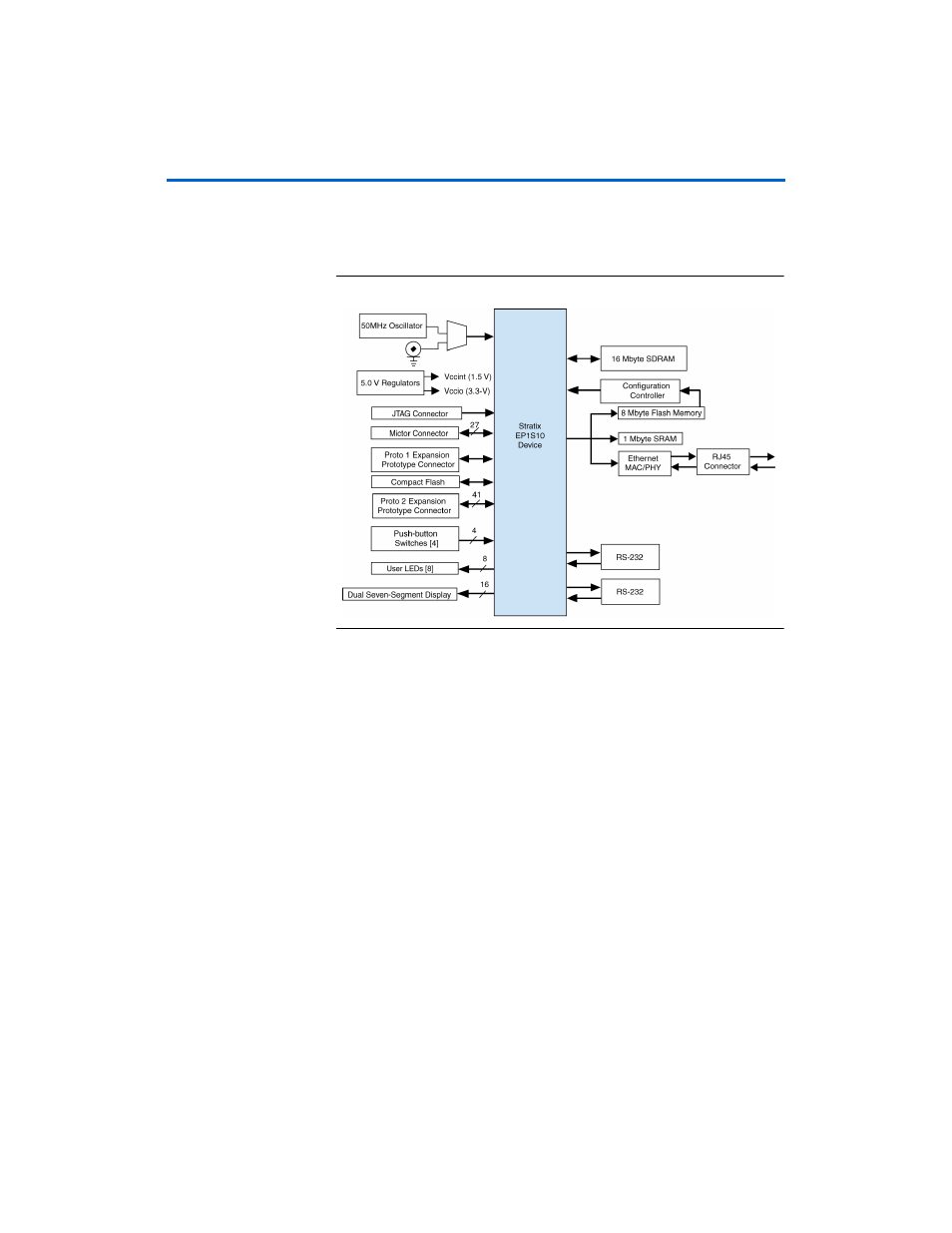

Block Diagram

shows a block diagram of the Stratix board.

Figure 1–1. Nios Development Board, Stratix Edition Block Diagram

Default Reference Design

When power is applied to the board, on-board logic configures the Stratix

FPGA using hardware configuration data stored in flash memory. When

the device is configured, the Nios II processor design in the FPGA wakes

up and begins executing boot code from flash memory.

The board is factory-programmed with a default reference design. This

reference design is a web server that delivers web pages via the Ethernet

port. For further information on the default reference design, see

“Connecting to the Board via Ethernet” on page C–1

Restoring the Default Reference Design to the Board

In the course of development, you may overwrite or erase the flash

memory space containing the default reference design. Altera provides

the flash image for the default reference design so you can return the

board to its default state. See

Appendix B, Restoring the Factory

for more information.