The stratix ep1s10 device, Flash memory device – Altera Nios Development Board User Manual

Page 12

1–4

Altera

Corporation

Nios Development Board Reference Manual, Stratix Edition

September 2004

The Stratix EP1S10 Device

The Stratix

EP1S10 Device

U53 is a Stratix EP1S10F780C6 device in a 780-pin

FineLine BGA

package.

lists the Stratix device features.

The development board provides two separate methods for configuring

the Stratix device:

1.

Using the Quartus II software running on a host computer, a

designer configures the device directly via an Altera download

cable connected to the Stratix header (J24).

2.

When power is applied to the board, a configuration controller

device (U3) attempts to configure the Stratix device with hardware

configuration data stored in flash memory. For more information on

the configuration controller, see

“Configuration Controller Device

.

f

See the Altera Stratix literature page for Stratix-related documentation

including Stratix EP1S10 pin out data at www.altera.com/literature/ lit-

stx.html

.

Flash Memory

Device

U5 is an 8 Mbyte AMD AM29LV065D flash memory device connected to

the Stratix device and can be used for two purposes:

1.

A Nios II embedded processor implemented on the Stratix device

can use the flash as general-purpose readable memory and non-

volatile storage.

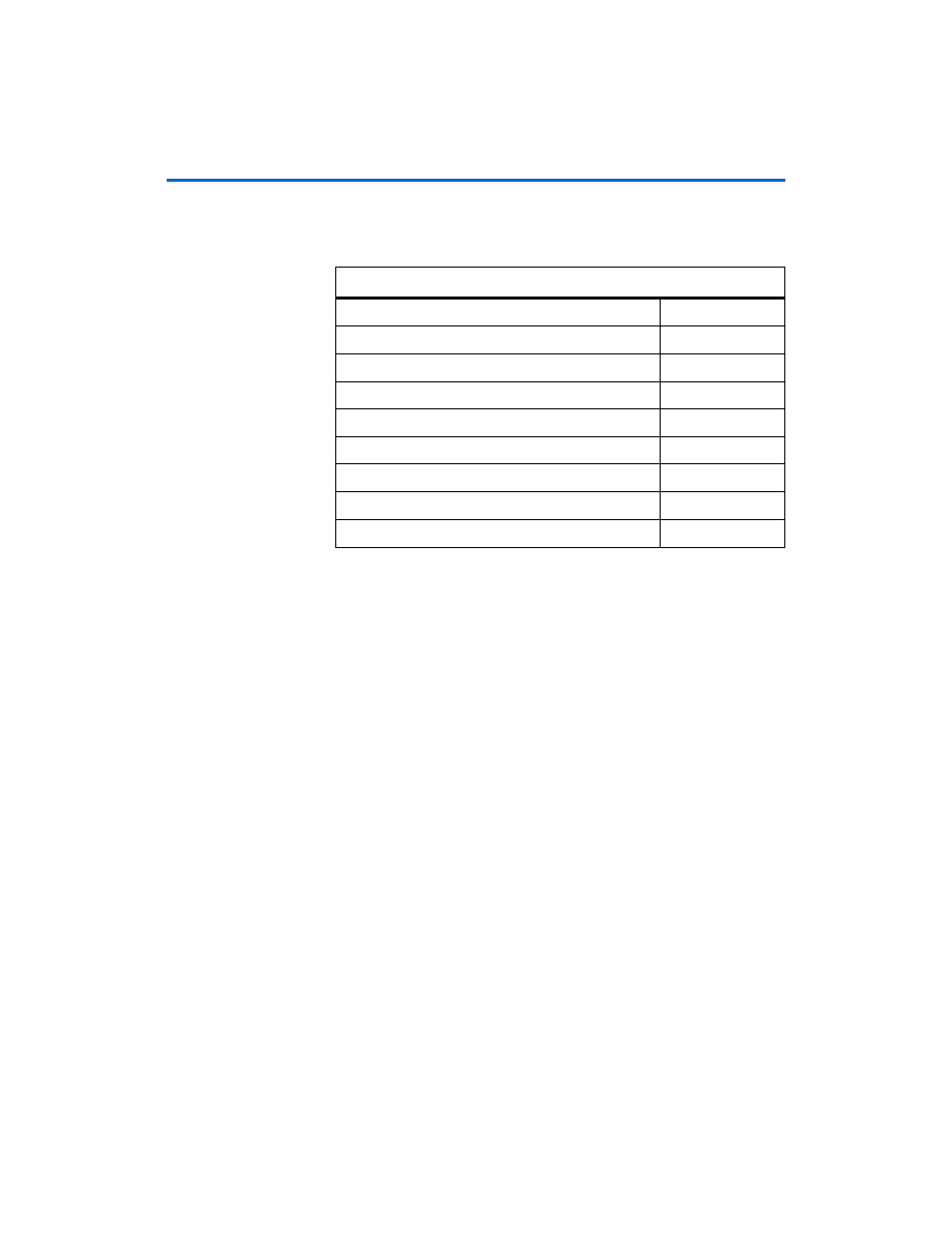

Table 1–1. Stratix EP1S10 Device Features

LEs

10,570

M512 RAM blocks (32 X 18 bits)

94

M4K RAM blocks (128 X 36 bits)

60

M-RAM blocks (4K X 144 bits)

1

Total RAM bits

920,448

DSP blocks

6

Embedded multipliers

48

PLLS

6

Maximum user I/O pins

426