Mictor connector, Mictor connector –16, Figure 1–10 – Altera Nios Development Board User Manual

Page 24

1–16

Altera

Corporation

Nios Development Board Reference Manual, Stratix Edition

September 2004

Mictor Connector

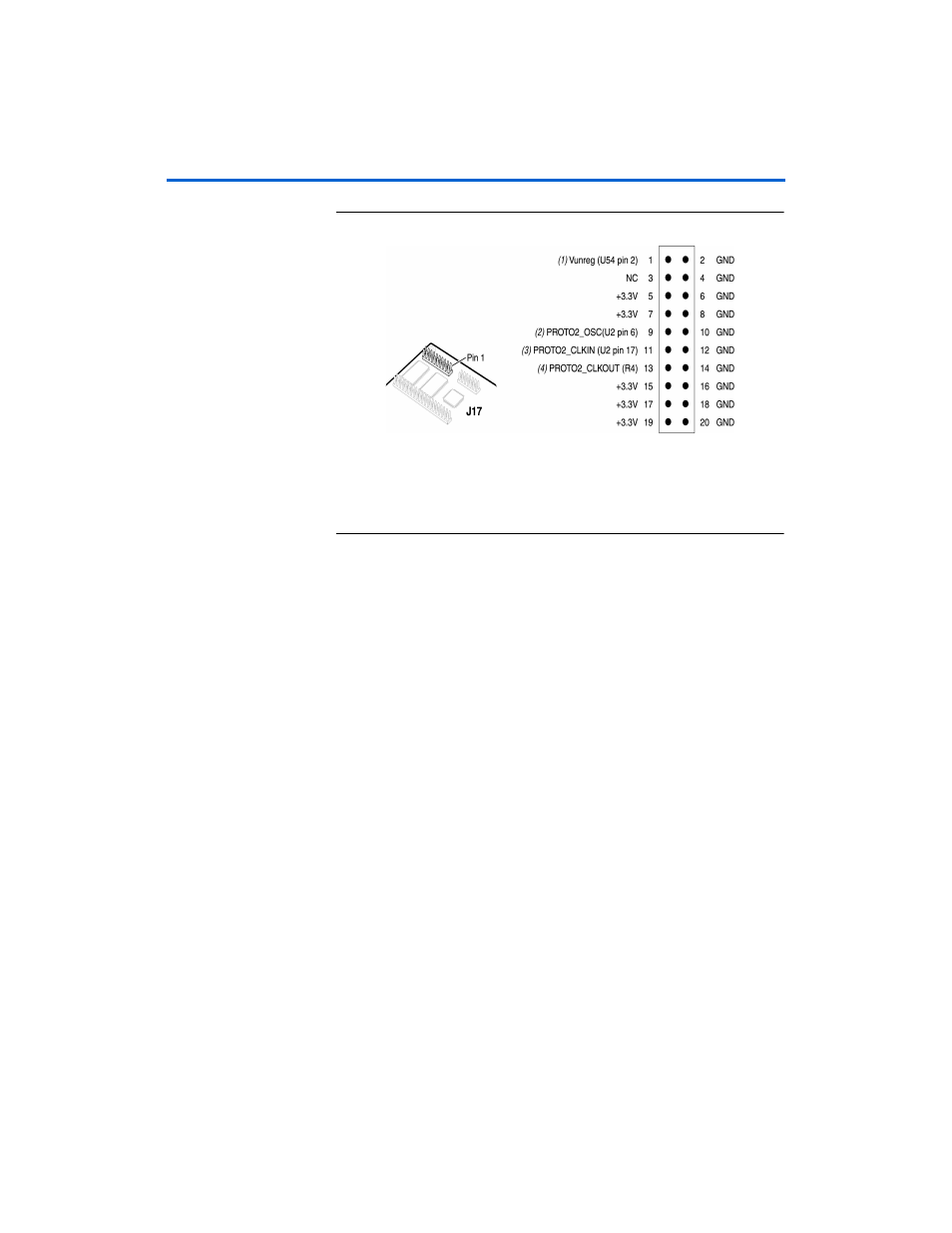

Figure 1–10. Expansion Prototype Connector - J17

(1)

Unregulated voltage from AC to DC power transformer

(2)

Clk from board oscillator

(3)

Clk from FPGA via buffer

(4)

Clk output from protocard to FPGA

Mictor

Connector

The Mictor connector (J25) can be used to transmit up to 27 high-speed

I/O signals with very low noise via a shielded Mictor cable. J25 is used as

a debug port. Twenty five of the Mictor connector signals are used as data,

and two signals are used as clock input and clock output.

Most pins on J25 connect to I/O pins on the Stratix device (U53). For

systems that do not use the Mictor connector for debugging the Nios II

processor, any on-chip signals can be routed to I/O pins and probed at J25

via a Mictor cable. External scopes and logic analyzers can connect to J25

and analyze a large number of signals simultaneously.

f

For details on Nios II debugging products that use the Mictor connector,

see www.altera.com.

shows an example of an in-target system

analyzer ISA-Nios/T (sold separately) by First Silicon Solutions (FS2) Inc.

connected to the Mictor connector. For details see www.fs2.com.