Compactflash connector, Compactflash connector –5 – Altera Nios Development Board User Manual

Page 13

Altera Corporation

1–5

September 2004

Nios Development Board Reference Manual, Stratix Edition

Board Components

2.

The flash memory can hold a Stratix device configuration file that is

used by the configuration controller to load the Stratix device at

power-up.

“Configuration Controller Device (EPM7128AE)” on

for related information.

Hardware configuration data that implements the Nios II reference

design is pre-stored in this flash memory. The factory programmed

Nios II reference design, once loaded, can identify the 8 Mbyte flash

memory in its address space, and can program new data (either new

Stratix configuration data, Nios II embedded processor software, or both)

into flash memory. The Nios II embedded processor software includes

subroutines for writing and erasing this specific type of AMD flash

memory.

The flash memory device shares address and data connections with the

SRAM chips and the Ethernet MAC/PHY chip. For shared bus

information, see

.

f

See www.amd.com for detailed information about the flash memory

device.

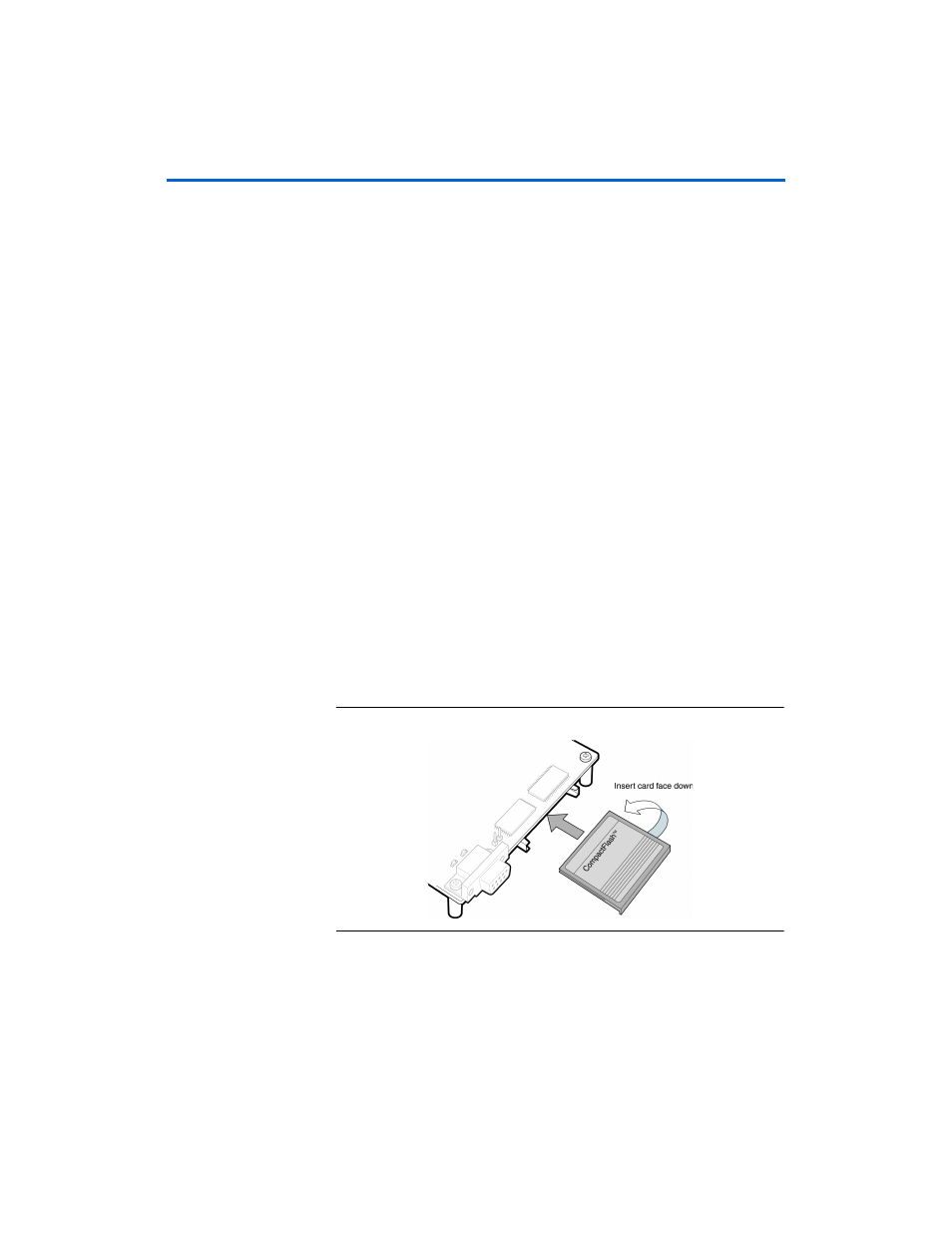

CompactFlash

Connector

The CompactFlash connector header (CON3) enables hardware designs

to access a CompactFlash card. See

. The following two access

modes are supported:

■

ATA (hot swappable mode)

■

IDE (IDE hard disk mode)

Figure 1–3. CompactFlash Connector

Most pins of CON3 connect to I/O pins on the FPGA. The following pins

have special connections: