Nios development board components, Nios development board components –3 – Altera Nios Development Board User Manual

Page 11

Altera Corporation

1–3

September 2004

Nios Development Board Reference Manual, Stratix Edition

Board Components

Nios

Development

Board

Components

This section contains a brief overview of several important components

on the Nios development board (see

). Links to the component

manufacturers are included where available.

A complete set of schematics, a physical layout database, and GERBER

files for the development board are installed in the Nios II development

kit documents directory.

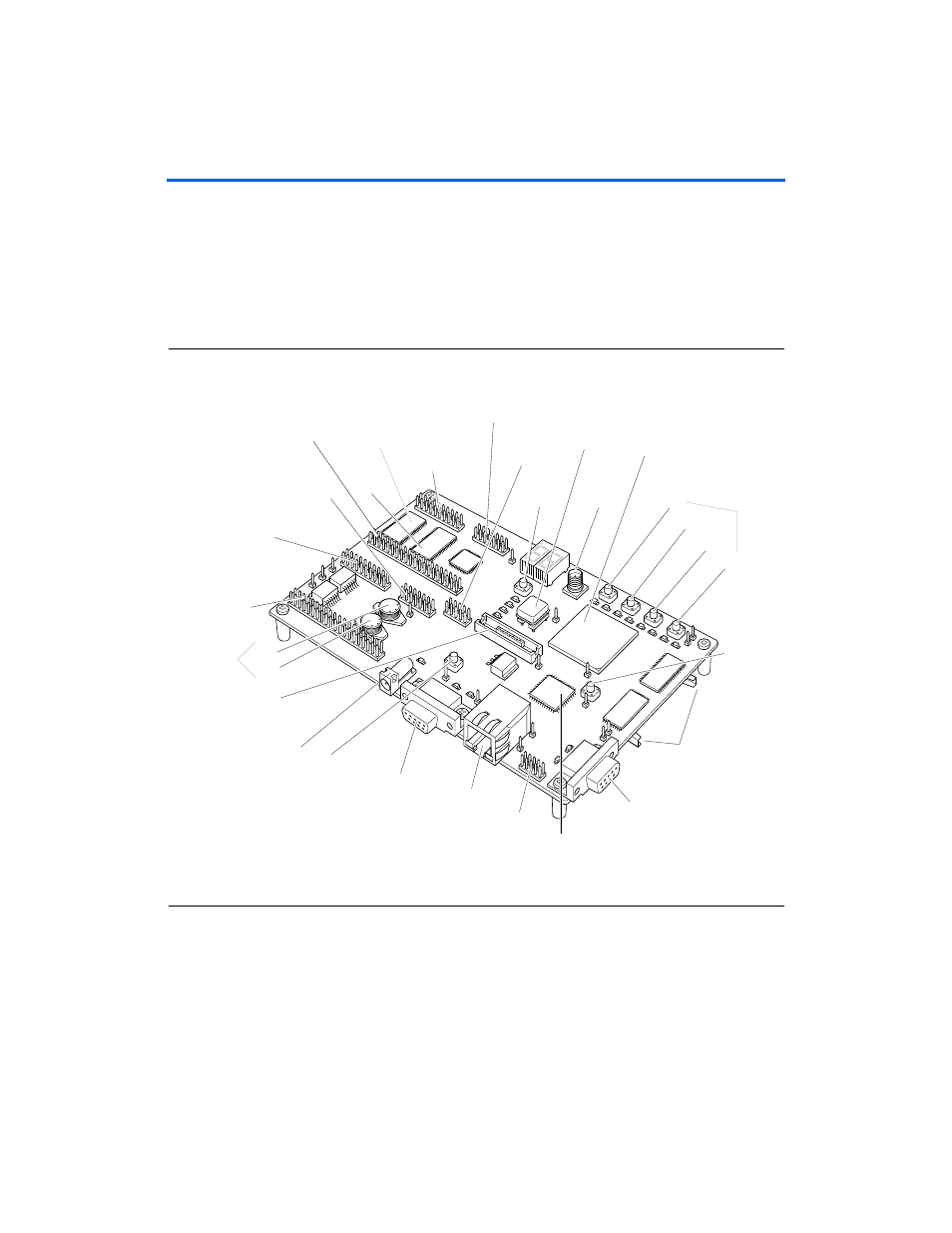

Figure 1–2. Nios Development Board

(J27)

Serial port

connector

(J19)

Serial port

connector

(RJ1)

RJ-45

connector

(J24)

10-pin JTAG

header for

Stratix

FPGA

(J5)

10-pin JTAG

header for

MAX device

(J16)

40-pin header for

3.3/5.0 volt prototype

connector

(PROTO2)

(J12)

14-pin header for

3.3/5.0 volt

prototype

connector

(PROTO1)

(J11)

40-pin header for

3.3/5.0 volt prototype

connector

(PROTO1)

(L11)

(L10)

(J25)

Debug mictor

connector

(SW10)

Reset Config

button

(J13)

20-pin header for

3.3/5.0 volt prototype

connector

(PROTO1)

(J15)

14-pin header for 3.3/5.0 volt

prototype connector

(PROTO2)

(J4)

External

clock

input

(J17)

20-pin header for

3.3/5.0 volt

prototype

connector

(PROTO2)

(SW0)

(SW8)

CPU reset

button

(CON3)

CompactFlash

connector header

(SW1)

(SW2)

(SW3)

(SW9)

Safe Config

Button

(Y2)

Crystal

Oscillator

(U53)

Stratix

EP1S10F780C6

device

(J26 )

DC jack

(SW3, SW2,

SW1, SW0)

User push-button

switches

(L11, L10)

Inductors

(U4)

Ethernet

PHY/MAC

device

(U35)

SRAM

device

(U36)

SRAM

device