User hardware image, Safe hardware image – Altera Nios Development Board User Manual

Page 31

Altera Corporation

1–23

September 2004

Nios Development Board Reference Manual, Stratix Edition

Board Components

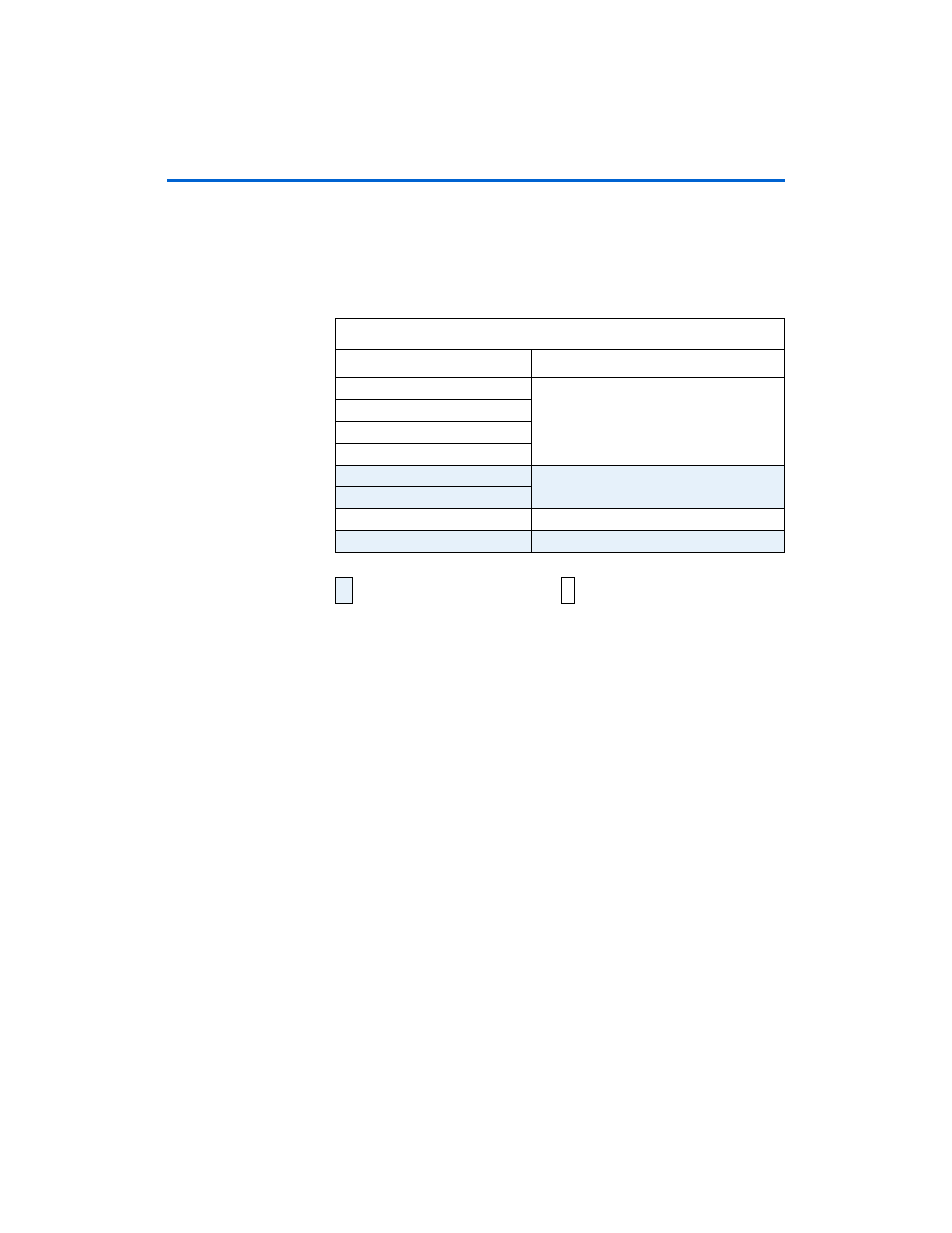

In the factory-programmed state, the upper four (4) MBbytes of flash

memory are used to store either FPGA configuration data or web-page

data. Your application software may safely use the lower half (4 MBytes)

of flash memory without interfering with FPGA configuration or web-

server operation.

1

The factory-programmed reference design implements a web

server. Network settings and web pages are pre-programmed in

the flash memory, as shown in

User Hardware Image

At power on, or when the Reset, Config button (SW10) is pressed, the

configuration controller reads user configuration data out of flash at

address 0x600000. This data, and suitable control signals, are used in an

attempt to configure the FGPA. FPGA configuration data written into this

region of flash memory is conventionally called the user hardware image.

Nios II development tools include documentation on how to create your

own user hardware image data and several facilities for burning your

user hardware image into flash memory.

Safe Hardware Image

If there is no valid user hardware image, or if SW9 (Safe Config) is

pressed, the configuration controller begins reading data out of flash at

address 0x700000. Any FPGA configuration data stored at this location is

conventionally called the safe hardware image. Your development board

was factory-programmed with a safe hardware image, plus additional

data located in the range 0x700000-0x7FFFFF, as shown in

.

Table 1–6. Flash Memory Allocation

Address (hex)

Flash Allocation

000000

4MB

100000

200000

300000

400000

Web Pages (2MB)

500000

600000

User Configuration Data (1 MB)

700000

Safe Configuration Data (1 MB)

Factory-programmed–do not erase

Available for user data.