Fft ip core avalon-st signals, Fft ip core avalon-st signals -17 – Altera FFT MegaCore Function User Manual

Page 40

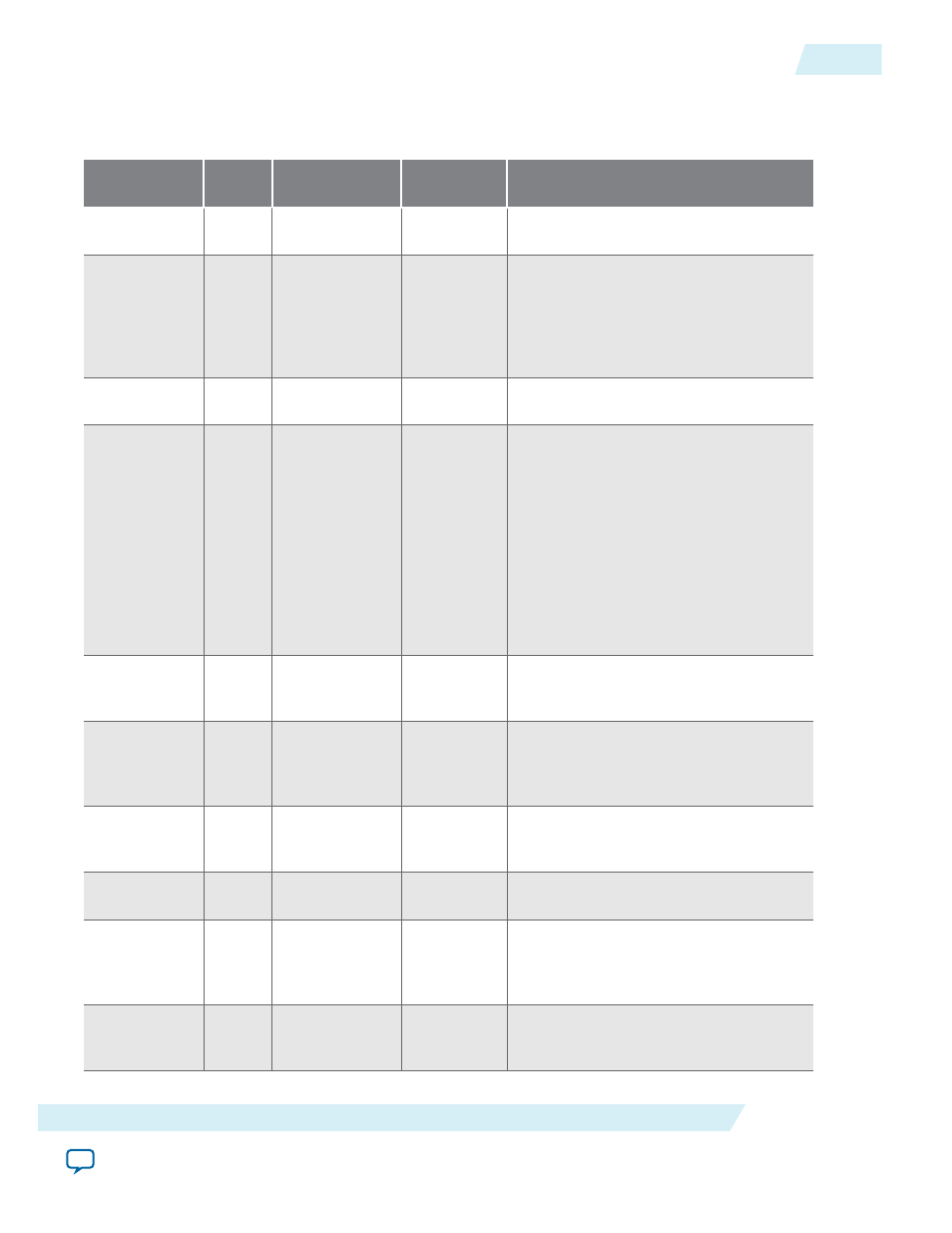

FFT IP Core Avalon-ST Signals

Table 3-6: Avalon-ST Signals

Signal Name

Directio

n

Avalon-ST Type

Size

Description

clk

Input

clk

1

Clock signal that clocks all internal FFT

engine components.

reset_n

Input

reset_n

1

Active-low asynchronous reset

signal.This signal can be asserted

asynchronously, but must remain

asserted at least one

clk

clock cycle and

must be deasserted synchronously with

clk

.

sink_eop

Input

endofpacket

1

Indicates the end of the incoming FFT

frame.

sink_error

Input

error

2

Indicates an error has occurred in an

upstream module, because of an illegal

usage of the Avalon-ST protocol. The

following errors are defined:

• 00 = no error

• 01 = missing start of packet (SOP)

• 10 = missing end of packet (EOP)

• 11 = unexpected EOP

If this signal is not used in upstream

modules, set to zero.

sink_imag

Input

data

data

precision

width

Imaginary input data, which represents

a signed number of data precision bits.

sink_ready

Output

ready

1

Asserted by the FFT engine when it can

accept data. It is not mandatory to

provide data to the FFT during ready

cycles.

sink_real

Input

data

data

precision

width

Real input data, which represents a

signed number of data precision bits.

sink_sop

Input

startofpacket

1

Indicates the start of the incoming FFT

frame.

sink_valid

Input

valid

1

Asserted when data on the data bus is

valid. When

sink_valid

and

sink_

ready

are asserted, a data transfer takes

place..

sink_data

Input

data

Variable

In Qsys systems, this Avalon-ST-

compliant data bus includes all the

Avalon-ST input data signals.

UG-FFT

2014.12.15

FFT IP Core Avalon-ST Signals

3-17

FFT IP Core Functional Description

Altera Corporation