Fft processor engines, Quad-output fft engine, Fft processor engines -3 – Altera FFT MegaCore Function User Manual

Page 26: Quad-output fft engine -3

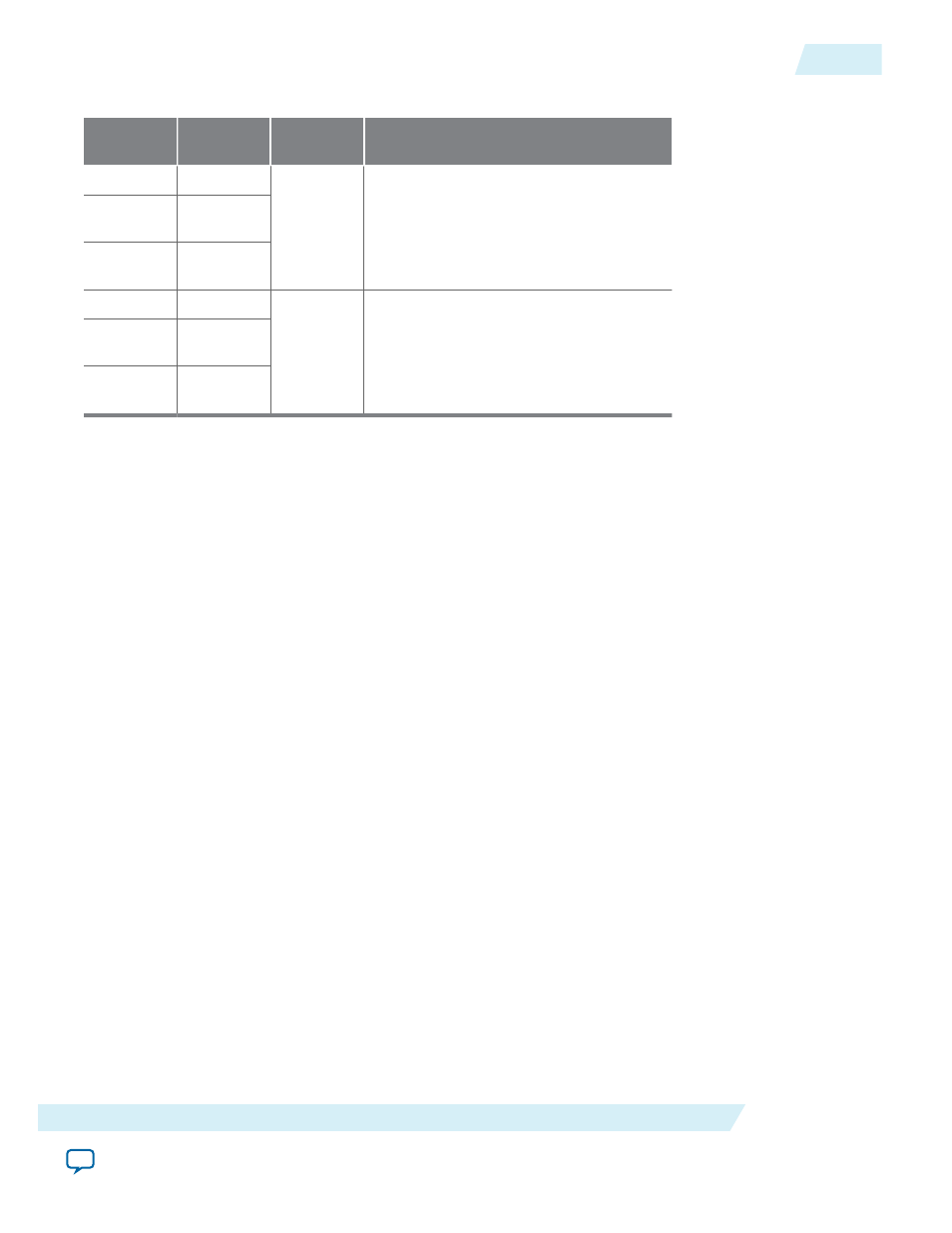

Table 3-1: Input and Output Order Options

Input Order

Output

Order

Mode

Comments

Natural Bit reversed

Engine-

only

Requires minimum memory and

minimum latency.

Bit

reversed

Natural

DC-

centered

Bit-

reversed

Natural Natural

Engine with

bit-reversal

At the output, requires an extra N

complex memory words and an

additional N clock cycles latency, where

N is the size of the transform.

Bit

reversed

Bit

reversed

DC-

centered

Natural

Some applications for the FFT require an FFT > user operation > IFFT chain. In this case, choosing the

input order and output order carefully can lead to significant memory and latency savings. For example,

consider where the input to the first FFT is in natural order and the output is in bit-reversed order (FFT is

operating in engine-only mode). In this example, if the IFFT operation is configured to accept bit-

reversed inputs and produces natural order outputs (IFFT is operating in engine-only mode), only the

minimum amount of memory is required, which provides a saving of N complex memory words, and a

latency saving of N clock cycles, where N is the size of the current transform.

FFT Processor Engines

You can parameterize the FFT MegaCore function to use either quad-output or single-output engines. To

increase the overall throughput of the FFT MegaCore function, you may also use multiple parallel engines

of a variation.

Quad-Output FFT Engine

To minimize transform time, use a quad-output FFT engine. Quad-output refers to the throughput of the

internal FFT butterfly processor. The engine implementation computes all four radix-4 butterfly complex

outputs in a single clock cycle.

UG-FFT

2014.12.15

FFT Processor Engines

3-3

FFT IP Core Functional Description

Altera Corporation