Fft ip core interfaces and signals, Avalon-st interfaces in dsp ip cores, Fft ip core interfaces and signals -16 – Altera FFT MegaCore Function User Manual

Page 39: Avalon-st interfaces in dsp ip cores -16

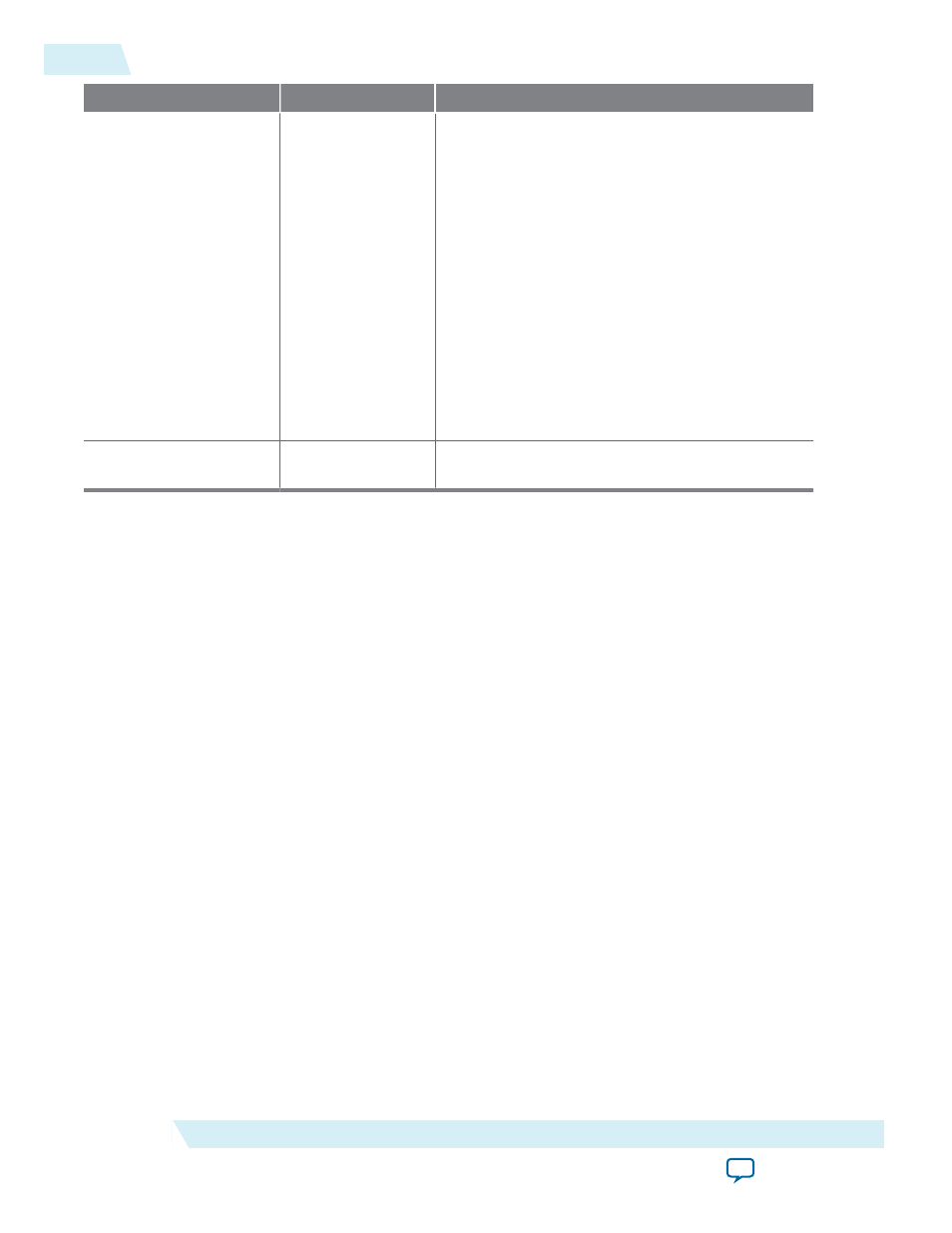

Parameter

Value

Description

DSP Block Resource

Optimization

On or Off

Turn on for multiplier structure optimizations.

These optimizations use different DSP block

configurations to pack multiply operations and

reduce DSP resource requirements. This

optimization may reduce F

MAX

because of the

structure of the specific configurations of the DSP

blocks when compared to the basic operation.

Specifically, on Stratix V devices, this optimiza‐

tion may also come at the expense of accuracy.

You can evaluate it using the MATLAB model

provided and bit wise accurate simulation models.

If you turn on DSP Block Resource Optimiza‐

tion and your variation has data precision

between 18 and 25 bits, inclusive, and twiddle

precision less than or equal to 18 bits, the FFT

MegaCore function configures the DSP blocks in

complex 18 x 25 multiplication mode.

Enable Hard Floating

Point Blocks

On or off

For Arria 10 devices and single-floating-point

FFTs only.

FFT IP Core Interfaces and Signals

The FFT IP core uses the Avalon-ST interface. You may achieve a higher clock rate by driving the source

ready signal

source_ready

of the FFT high, and not connecting the sink ready signal

sink_ready

.

The FFT MegaCore function has a

READY_LATENCY

value of zero.

Avalon-ST Interfaces in DSP IP Cores

Avalon-ST interfaces define a standard, flexible, and modular protocol for data transfers from a source

interface to a sink interface.

The input interface is an Avalon-ST sink and the output interface is an Avalon-ST source. The Avalon-ST

interface supports packet transfers with packets interleaved across multiple channels.

Avalon-ST interface signals can describe traditional streaming interfaces supporting a single stream of

data without knowledge of channels or packet boundaries. Such interfaces typically contain data, ready,

and valid signals. Avalon-ST interfaces can also support more complex protocols for burst and packet

transfers with packets interleaved across multiple channels. The Avalon-ST interface inherently synchro‐

nizes multichannel designs, which allows you to achieve efficient, time-multiplexed implementations

without having to implement complex control logic.

Avalon-ST interfaces support backpressure, which is a flow control mechanism where a sink can signal to

a source to stop sending data. The sink typically uses backpressure to stop the flow of data when its FIFO

buffers are full or when it has congestion on its output.

Related Information

•

3-16

FFT IP Core Interfaces and Signals

UG-FFT

2014.12.15

Altera Corporation

FFT IP Core Functional Description