Single-output fft engine, Single-output fft engine -4 – Altera FFT MegaCore Function User Manual

Page 27

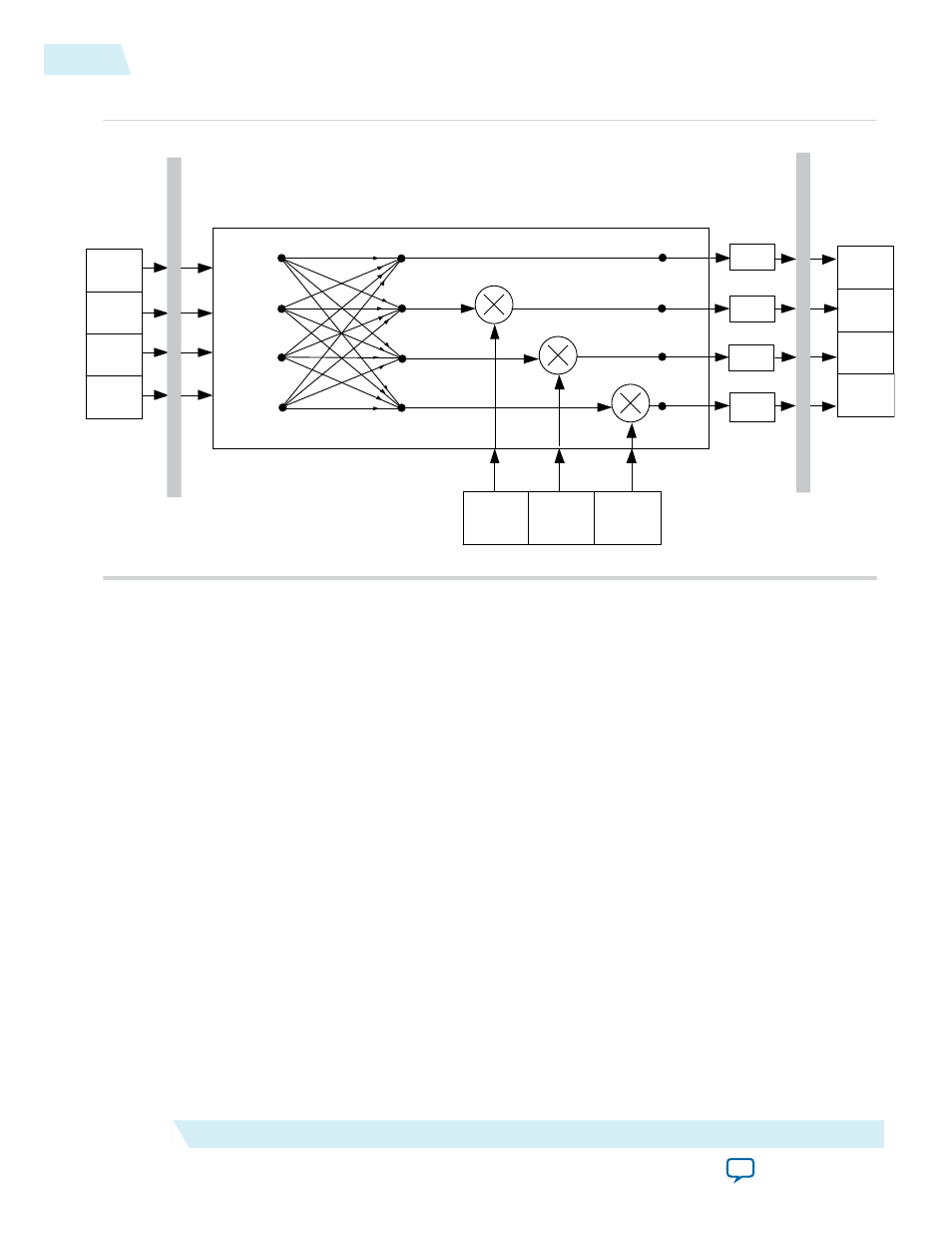

Figure 3-1: Quad-Output FFT Engine

ROM

0

FFT Engine

H[k,0]

H[k,1]

H[k,2]

H[k,3]

G[k,0]

G[k,1]

G[k,2]

G[k,3]

x[k,0]

x[k,1]

x[k,2]

x[k,3]

-j

-1 j

-1

-1

j

-1

-j

RAM

A1

RAM

A0

RAM

A2

RAM

A3

BFPU

BFPU

BFPU

BFPU

SW

SW

RAM

A1

RAM

A0

RAM

A2

RAM

A3

ROM

1

ROM

2

The FFT reads complex data samples x[k,m] from internal memory in parallel and reorders by switch

(SW). Next, the radix-4 butterfly processor processes the ordered samples to form the complex outputs

G[k,m]. Because of the inherent mathematics of the radix-4 DIF decomposition, only three complex

multipliers perform the three non-trivial twiddle-factor multiplications on the outputs of the butterfly

processor. To discern the maximum dynamic range of the samples, the block-floating point units (BFPU)

evaluate the four outputs in parallel. The FFT discards the appropriate LSBs and rounds and reorders the

complex values before writing them back to internal memory.

Single-Output FFT Engine

For the minimum-size FFT function, use a single-output engine. The term single-output refers to the

throughput of the internal FFT butterfly processor. In the engine, the FFT calculates a single butterfly

output per clock cycle, requiring a single complex multiplier.

3-4

Single-Output FFT Engine

UG-FFT

2014.12.15

Altera Corporation

FFT IP Core Functional Description