Dsp builder design flow, Dsp builder design flow -8 – Altera FFT MegaCore Function User Manual

Page 22

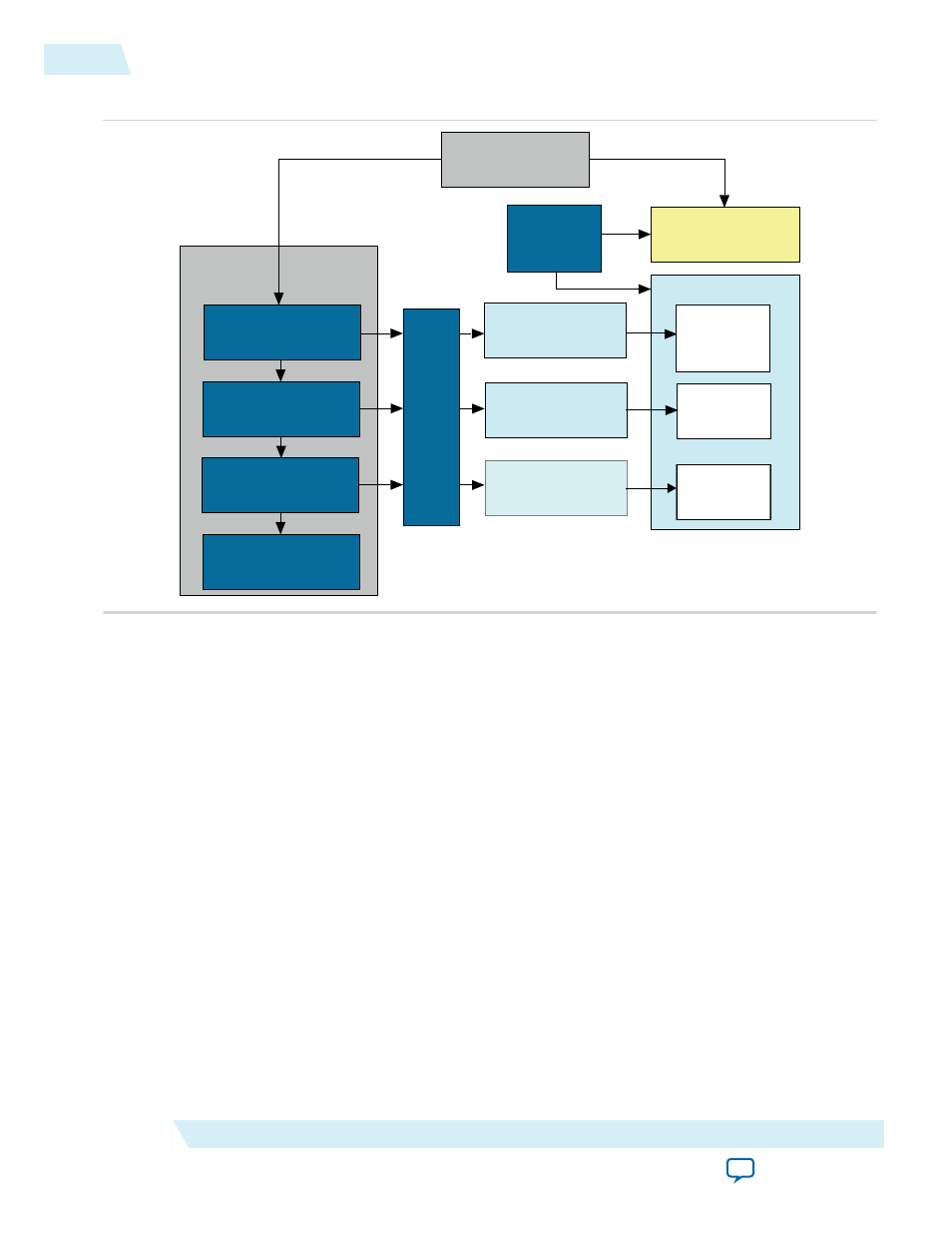

Figure 2-5: Simulation in Quartus II Design Flow

Post-fit timing

simulation netlist

Post-fit timing

simulation

(3)

Post-fit functional

simulation netlist

Post-fit functional

simulation

Analysis & Synthesis

Fitter

(place-and-route)

TimeQuest Timing Analyzer

Device Programmer

Quartus II

Design Flow

Gate-Level Simulation

Post-synthesis

functional

simulation

Post-synthesis functional

simulation netlist

(Optional) Post-fit

timing simulation

RTL Simulation

Design Entry

(HDL, Qsys, DSP Builder)

Altera Simulation

Models

EDA

Netlist

Writer

Note: Post-fit timing simulation is supported only for Stratix IV and Cyclone IV devices in the current

version of the Quartus II software. Altera IP supports a variety of simulation models, including

simulation-specific IP functional simulation models and encrypted RTL models, and plain text

RTL models. These are all cycle-accurate models. The models support fast functional simulation of

your IP core instance using industry-standard VHDL or Verilog HDL simulators. For some cores,

only the plain text RTL model is generated, and you can simulate that model. Use the simulation

models only for simulation and not for synthesis or any other purposes. Using these models for

synthesis creates a nonfunctional design.

Related Information

DSP Builder Design Flow

DSP Builder shortens digital signal processing (DSP) design cycles by helping you create the hardware

representation of a DSP design in an algorithm-friendly development environment.

This IP core supports DSP Builder. Use the DSP Builder flow if you want to create a DSP Builder model

that includes an IP core variation; use IP Catalog if you want to create an IP core variation that you can

instantiate manually in your design. For more information about the DSP Builder flow, refer to the

2-8

DSP Builder Design Flow

UG-FFT

2014.12.15

Altera Corporation

FFT IP Core Getting Started