Rockwell Automation 1746-HSCE2 Multi-Channel High Speed Counter Module User Manual

Page 90

Publication 1746-UM002B-EN-P - August 2004

5-8 Start Up, Operation, Troubleshooting, and Debug Mode

Figure 5.3 Required Bits for Module Setup and Counter Configuration Blocks

The debug view of this block shows the range allocation of all four

counters. The fourth counter is shown in word 5. The PRA bit

(word 0, bit 08) is never set.

In the Counter Configuration Block

The required bits for debug mode in the Counter Configuration Block

are the transmit bit, the debug bit, and the block type byte. Bits 13

and 14 must be zero. The values of words 1 through 7 are ignored by

the module while in debug mode. The PGM(n) bits (word 0, bits 08 to

11) are never set in this block.

Figure 5.4 Required Bits for Counter Configuration Block

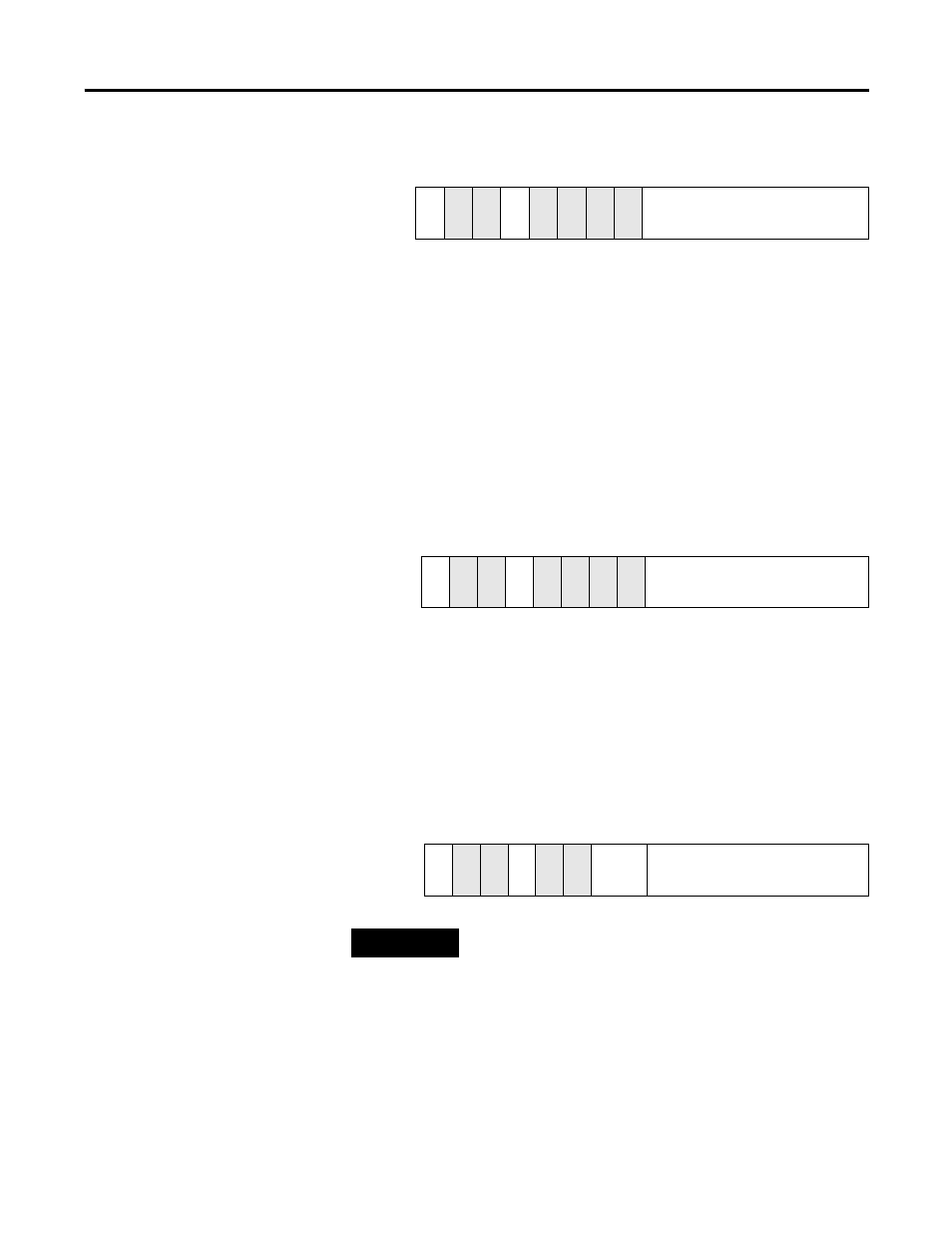

In the Minimum/Maximum Count Value Block

For this block, the transmit bit, the debug bit, the block type byte, and

the counter number are required for each configured counter. Word 0

must be used for each configured counter individually. Bit 10 is

ignored and bits 11, 13, and 14 must be zero. The values of words 1

through 7 are ignored by the module while in debug mode.

Figure 5.5 Required Bits for Min./Max. Count Value Block

15 14

13 12 11

10 09 08

07 06 05

04 03 02

01 00

Word 0

TRMT

0

0

DEBUG

0

0

0

0

BLOCK TYPE

15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

Word 0

TRMT

0

0

DEBUG

0

0

0

0

BLOCK TYPE

15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

Word 0

TRMT

0

0

DEB

U

G

0

X

CNTR

No.

BLOCK TYPE

TIP

If the counter number entered is not valid, the

debug mode returns a programming error.