Ordering information, References, Revision history – Cirrus Logic CS42L52 User Manual

Page 81

DS680F2

81

CS42L52

3/1/13

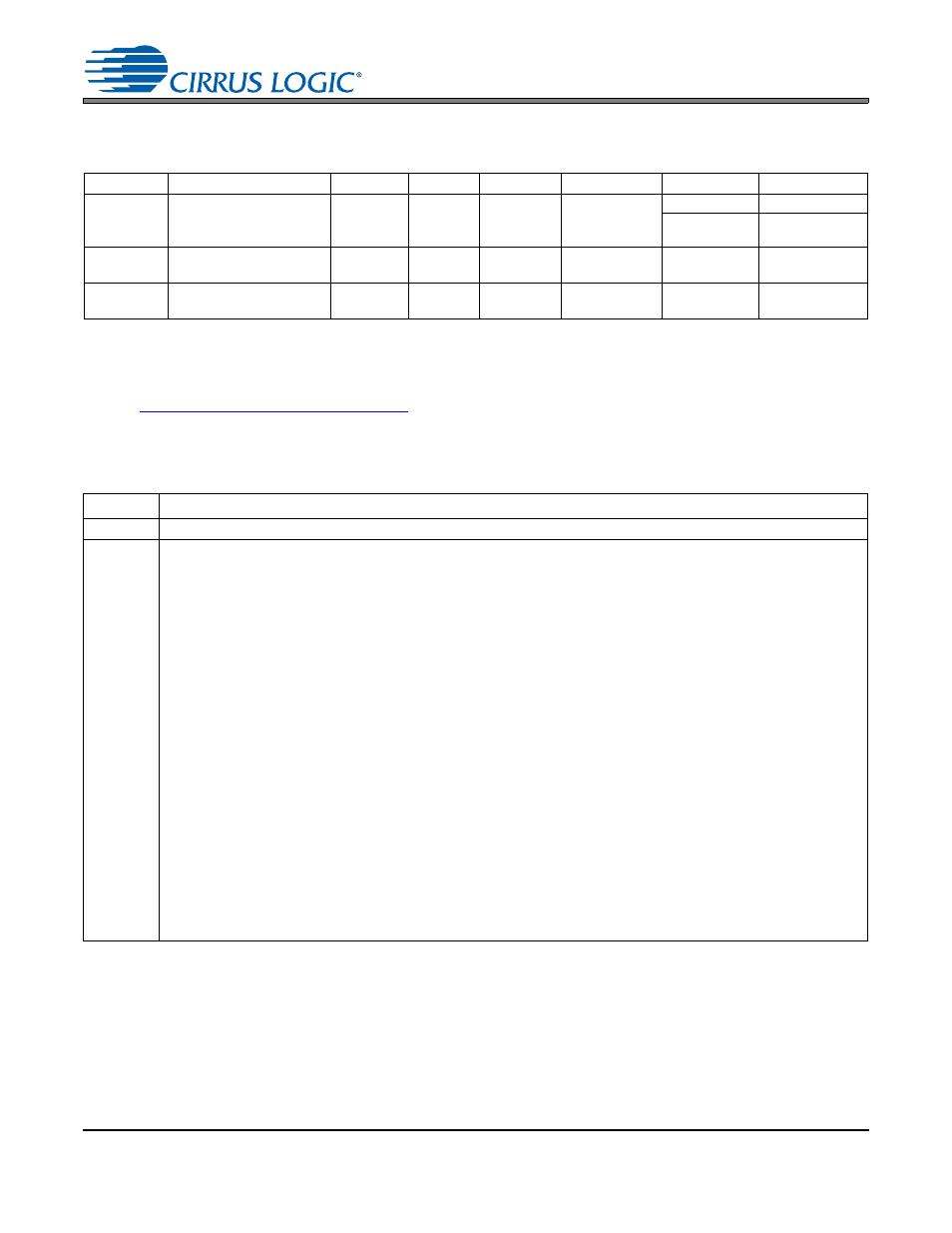

13.ORDERING INFORMATION

14.REFERENCES

1.

Philips Semiconductor, The I²C-Bus Specification: Version 2.1, January 2000.

15.REVISION HISTORY

Product

Description

Package Pb-Free

Grade

Temp Range

Container

Order #

CS42L52

Low-Power, Stereo

CODEC with Headphone

and Speaker Amps

40L-QFN

Yes

Commercial -40 to +85° C

Rail

CS42L52-CNZ

Tape and Reel CS42L52-CNZR

CDB42L52

CS42L52 Evaluation

Board

-

No

-

-

-

CDB42L52

CRD42L52

CS42L52

Reference

Design

-

No

-

-

-

CRD42L52

Revision

Changes

F1

Initial draft

F2

Removed the Automotive specification.

Added AD0 characteristics to

“I/O Pin Characteristics” on page 10

Figure 1. Typical Connection Diagram on page 11

.

Updated the V

IH

specification for VL = 1.8 V in

“Digital Interface Specifications and Characteristics” on page 22

to exclude support of a 384x MCLK to LRCK ratio.

Added register commands for entering and exiting DSP 16-bit, 8 kHz Fs, SCLK = MCLK, master mode in section

Section 4.9 “Recommended Power-up Sequence” on page 37

.

Section 4.10 “Recommended Power-Down Sequence” on page 37

.

Added a description of the AD0 pin to

.

Added AD0 detail to

Figure 20. Control Port Timing, I²C Write on page 38

and

Figure 21. Control Port Timing, I²C

Updated the first paragraph in

“Register Quick Reference” on page 40

to allow for data sheet-specified control-

writes to reserved registers.

Removed I²C address heading row from

“Register Quick Reference” on page 40

.

.

Updated table in

.

“Digital Soft Ramp” on page 53

“Digital Zero Cross” on page 53

Added notes

for ALC configuration in

“ALC Enable and Attack Rate (Address 2Ah)” on page 67

Corrected the E2 scale in the package drawing in

“Package Dimensions” on page 80

.