3 tri-state serial port interface, 4 speaker/headphone switch invert, 5 mic bias level – Cirrus Logic CS42L52 User Manual

Page 48: 1 adc input select, P 48

48

DS680F2

CS42L52

3/1/13

6.7.3

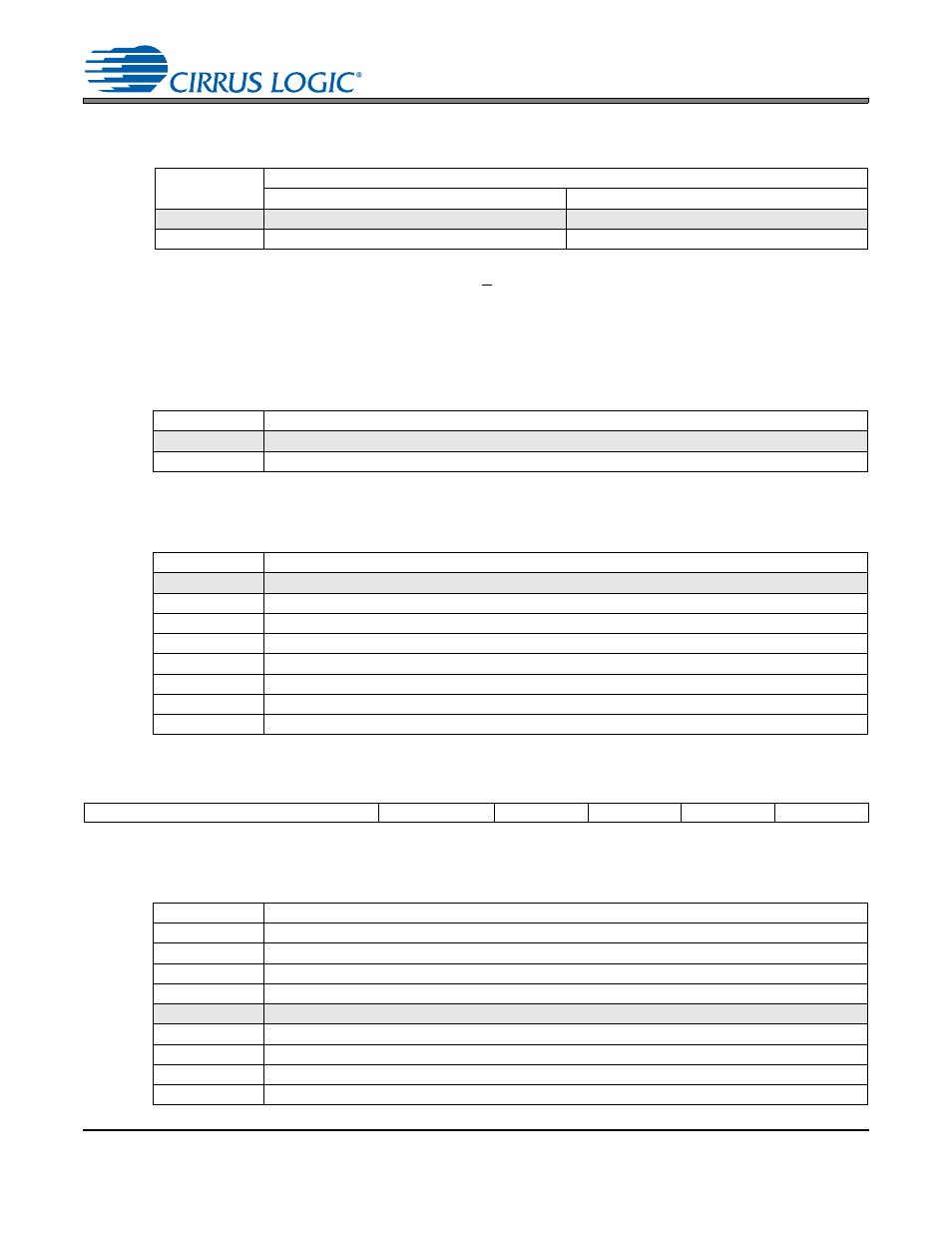

Tri-State Serial Port Interface

Determines the state of the serial port drivers.

Notes:

1.

Slave/Master Mode is determined by the M/S bit in

“Master/Slave Mode” on page 46

2.

When the serial port is tri-stated in master mode, the ADC and DAC serial ports are clocked internally.

6.7.4

Speaker/Headphone Switch Invert

Determines the control signal polarity of the SPK/HP_SW pin.

6.7.5

MIC Bias Level

Sets the output voltage level on the MICBIAS output pin.

6.8

Input x Select: ADCA and PGAA (Address 08h), ADCB and PGAB (Address 09h)

6.8.1

ADC Input Select

Selects the specified analog input signal into ADCx.

3ST_SP

Serial Port Status

Slave Mode

Master Mode

0

Serial Port clocks are inputs and SDOUT is output

Serial Port clocks and SDOUT are outputs

1

Serial Port clocks are inputs and SDOUT is HI-Z

Serial Port clocks and SDOUT are HI-Z

INV_SWCH

SPK/HP_SW pin 6 Control

0

Not inverted

1

Inverted

BIASLVL[2:0]

Output Bias Level

000

0.5 x VA

001

0.6 x VA

010

0.7 x VA

011

0.8 x VA

100

0.83 x VA

101

0.91 x VA

110

Reserved

111

Reserved

7

6

5

4

3

2

1

0

ADCASEL2

ADCASEL1

ADCASEL0

PGAASEL5

PGAASEL4

PGAASEL3

PGAASEL2

PGAASEL1

ADCxSEL[2:0]

Selected Input to ADCx

000

AIN1x

001

AIN2x

010

AIN3x

011

AIN4x

100

PGAx - Use PGAxSEL bits (

“PGA Input Mapping” on page 49

) to select input channels

101

Reserved

110

Reserved

111

Reserved

Application: