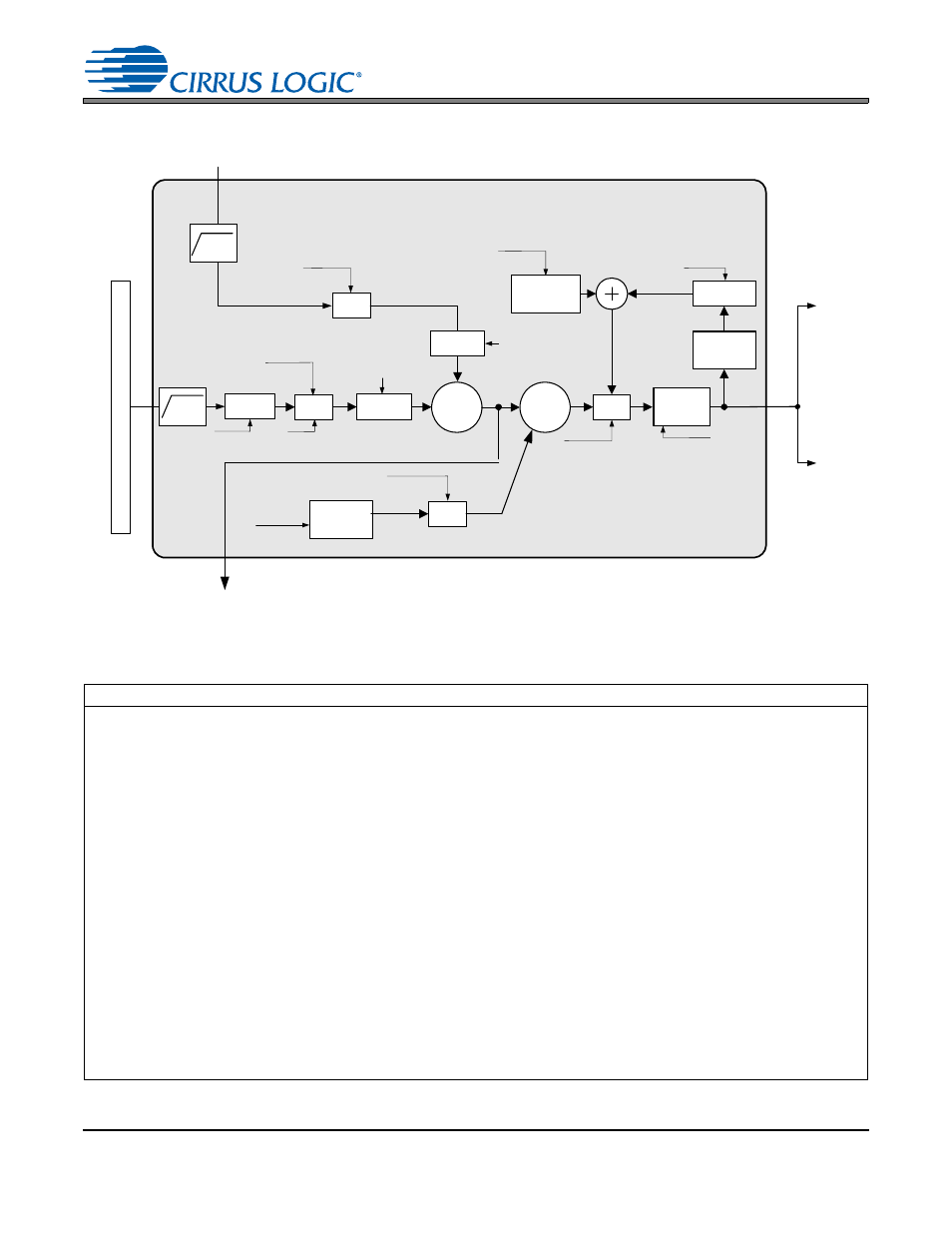

3 analog outputs, Figure 10. dsp engine signal flow, Fixed function dsp – Cirrus Logic CS42L52 User Manual

Page 28

28

DS680F2

CS42L52

3/1/13

4.3

Analog Outputs

Referenced Control

Register Location

DSP

DEEMPH .............................

PMIXxMUTE........................

PMIXxVOL[6:0]....................

INV_PCMx...........................

PCMxSWAP[1:0] .................

AMIXxMUTE........................

AMIXxVOL[6:0]....................

ADCxSWAP[1:0]..................

MSTxVOL[7:0].....................

MSTxMUTE.........................

DIGSFT ...............................

DIGZC .................................

PLYBCKB=A........................

TC_EN.................................

BASS_CF[1:0] .....................

TREB_CF[1:0] .....................

BASS[3:0]............................

TREB[3:0]............................

LIMIT ...................................

LIMSRDIS ...........................

LIMZCDIS............................

LMAX[2:0]............................

CUSH[2:0] ...........................

LIMARATE[7:0]....................

LIMRRATE[7:0] ...................

“HP/Speaker De-emphasis” on page 53

“PCM Mixer Channel x Mute” on page 58

“PCM Mixer Channel x Volume” on page 58

“Invert PCM Signal Polarity” on page 52

“PCM Mix Channel Swap” on page 64

“ADC Mixer Channel x Mute” on page 58

“ADC Mixer Channel x Volume” on page 58

“ADC Mix Channel Swap” on page 64

“Master Volume Control” on page 63

“Master Playback Mute” on page 52

“Digital Soft Ramp” on page 53

“Digital Zero Cross” on page 53

“Playback Volume Setting B=A” on page 51

“Tone Control Enable” on page 62

“Bass Corner Frequency” on page 62

“Treble Corner Frequency” on page 62

“Bass Gain” on page 63

“Treble Gain” on page 62

“Peak Detect and Limiter” on page 66

“Limiter Soft Ramp Disable” on page 65

“Limiter Zero Cross Disable” on page 66

“Limiter Maximum Threshold” on page 65

“Limiter Cushion Threshold” on page 65

“Limiter Attack Rate” on page 67

“Limiter Release Rate” on page 66

Beep

Generator

VOL

Bass/

Treble/

Control

VOL

Peak

Detect

Limiter

Chnl Vol.

Settings

Channel

Swap

Demph

VOL

VOL

+12dB/-102dB

0.5dB steps

MSTAVOL[7:0]

MSTBVOL[7:0]

+12dB/-51.5dB

0.5dB steps

AMIXAMUTE

AMIXBMUTE

AMIXAVOL[6:0]

AMIXBVOL[6:0]

+12dB/-51.5dB

0.5dB steps

PMIXAMUTE

PMIXBMUTE

PMIXAVOL[6:0]

PMIXBVOL[6:0]

0dB/-50dB

2.0dB steps

BPVOL[4:0]

DEEMPH

TC_EN

BASS_CF[1:0]

TREB_CF[1:0]

BASS[3:0]

TREB[3:0]

+12.0dB/-10.5dB

1.5dB steps

Fixed Function DSP

MSTAMUTE

MSTBMUTE

DIGSFT

DIGZC

PLYBCKB=A

LIMARATE[7:0]

LIMRRATE[7:0]

LMAX[2:0]

CUSH[2:0]

LIMSRDIS

LIMZCDIS

LIMIT

PCMASWAP[1:0]

PCMBSWAP[1:0]

PC

M

Seria

l

In

te

rf

a

c

e

INPUTS FROM ADCA

and ADCB

OFFTIME[2:0]

ONTIME[3:0]

FREQ[3:0]

BEEP[1:0]

BEEPMIXDIS

Digital Mix to ADC

Serial Interface

Channel

Swap

INV_PCMA

INV_PCMB

ADCASWAP[1:0]

ADCBSWAP[1:0]

PWM

Modulator

DAC

Figure 10. DSP Engine Signal Flow