6 mclk divide by 2, 6 interface control 1 (address 06h), 1 master/slave mode – Cirrus Logic CS42L52 User Manual

Page 46: 2 sclk polarity, 3 adc interface format, 4 dsp mode, P 46

46

DS680F2

CS42L52

3/1/13

6.5.6

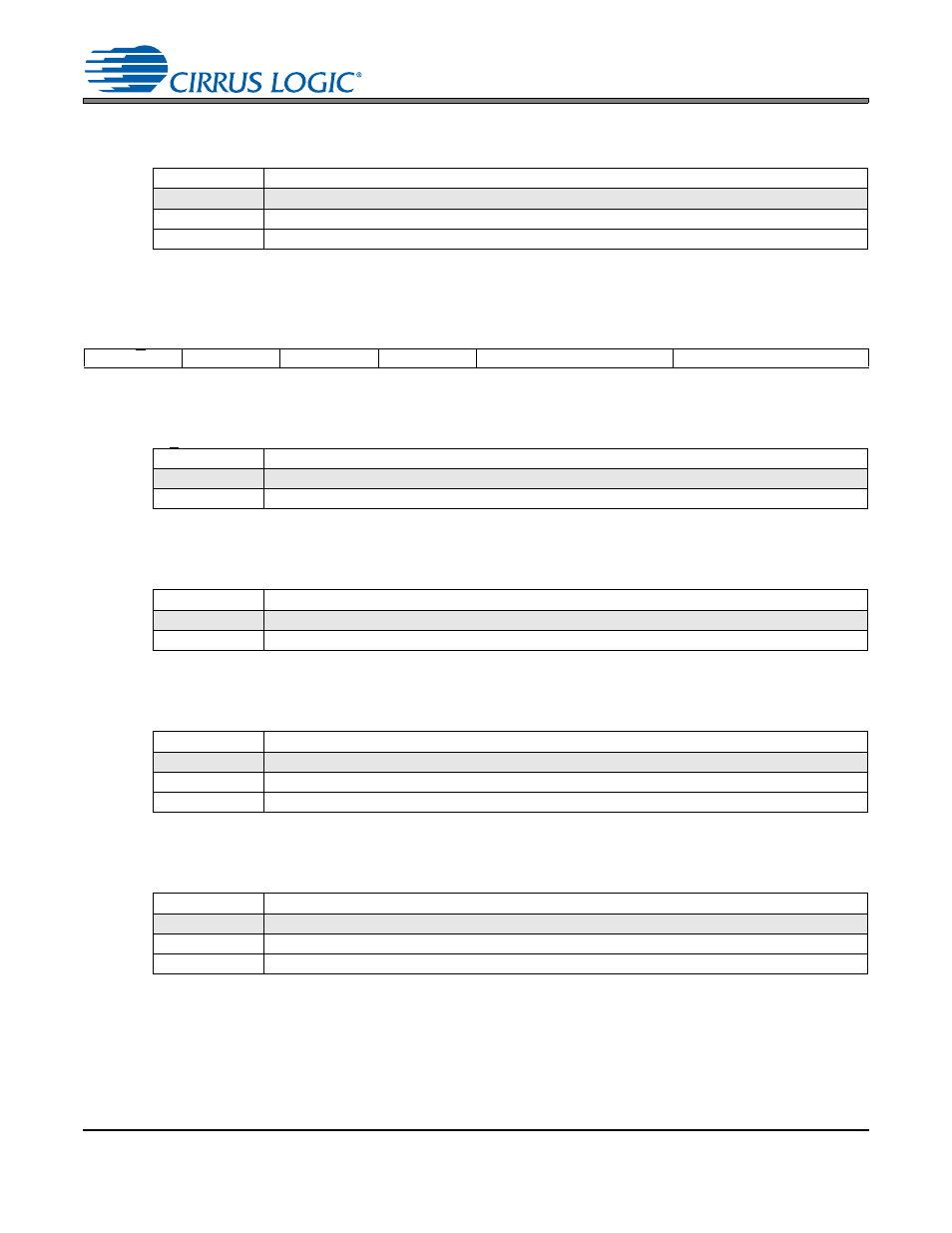

MCLK Divide By 2

Divides the input MCLK by 2 prior to all internal circuitry.

Note:

In slave mode, this bit is ignored when the AUTO bit (

) is disabled.

6.6

Interface Control 1 (Address 06h)

6.6.1

Master/Slave Mode

Configures the serial port I/O clocking.

6.6.2

SCLK Polarity

Configures the polarity of the SCLK signal.

6.6.3

ADC Interface Format

Configures the digital interface format for data on SDOUT.

6.6.4

DSP Mode

Configures a data-packed interface format for both the ADC and DAC.

Notes:

1.

Select the audio word length using the AWL[1:0] bits (

“Audio Word Length” on page 47

2.

The interface format for both the ADC and the DAC must be set to “Left-Justified” when DSP Mode

is enabled.

MCLKDIV2

MCLK signal into CODEC

0

No divide

1

Divided by 2

Application:

“Serial Port Clocking” on page 33

7

6

5

4

3

2

1

0

M/S

INV_SCLK

ADCDIF

DSP

DACDIF1

DACDIF0

AWL1

AWL0

M/S

Serial Port Clocks

0

Slave (input ONLY)

1

Master (output ONLY)

INV_SCLK

SCLK Polarity

0

Not Inverted

1

Inverted

ADCDIF

ADC Interface Format

0

Left Justified

1

I²S

Application:

“Digital Interface Formats” on page 35

DSP

DSP Mode

0

Disabled

1

Enabled

Application: