3 noise gate threshold and boost, 4 noise gate delay timing, 36 status (address 2eh) (read only) – Cirrus Logic CS42L52 User Manual

Page 70: 1 serial port clock error (read only), P 70

70

DS680F2

CS42L52

3/1/13

6.35.3

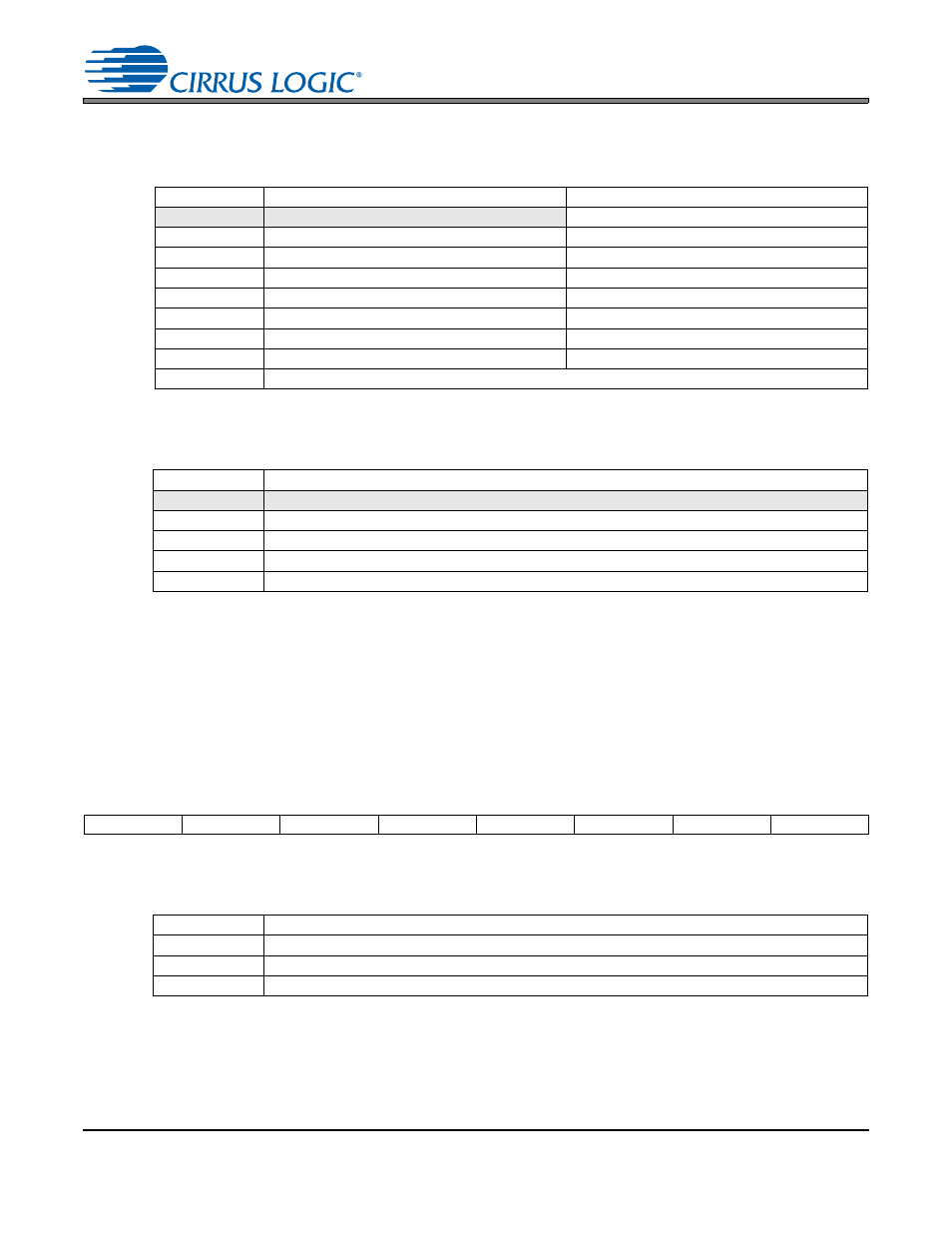

Noise Gate Threshold and Boost

THRESH sets the threshold level of the noise gate. Input signals below the threshold level will be attenu-

ated to -96 dB. NG_BOOST configures a +30 dB boost to the threshold settings.

6.35.4

Noise Gate Delay Timing

Sets the delay time before the noise gate attacks.

Note:

The Noise Gate attack rate is a function of the sampling frequency, Fs, and the ANLGSFTx (

x Analog Soft Ramp” on page 49

) and ANLGZCx (

“Ch. x Analog Zero Cross” on page 49

) setting unless

the respective disable bit (

“ALCx Soft Ramp Disable” on page 55

) is enabled.

6.36

Status (Address 2Eh) (Read Only)

For all bits in this register, a “1” means the associated error condition has occurred at least once since the

register was last read. A”0” means the associated error condition has NOT occurred since the last reading

of the register. Reading the register resets all bits to 0.

6.36.1

Serial Port Clock Error (Read Only)

Indicates the status of the MCLK to LRCK ratio.

Note:

On initial power up and application of clocks, this bit will report 1 as the serial port re-synchroniz-

es.

THRESH[2:0]

Minimum Setting

(NG_BOOST = 0)

Minimum Setting

(NG_BOOST = 1)

000

-64 dB

-34 dB

001

-67 dB

-37 dB

010

-70 dB

-40 dB

011

-73 dB

-43 dB

100

-76 dB

-46 dB

101

-82 dB

-52 dB

110

Reserved

-58 dB

111

Reserved

-64 dB

Application:

NGDELAY[1:0]

Delay Setting

00

50 ms

01

100 ms

10

150 ms

11

200 ms

Application:

7

6

5

4

3

2

1

0

Reserved

SPCLKERR

DSPAOVFL

DSPBOVFL

PCMAOVFL

PCMBOVFL

ADCAOVFL

ADCBOVFL

SPCLKERR

Serial Port Clock Status:

0

MCLK/LRCK ratio is valid.

1

MCLK/LRCK ratio is not valid.

Application: