22 interrupt mask 1 (address 1fh), 1 test mode error interrupt mask, 2 serial port error interrupt mask – Cirrus Logic CS4234 User Manual

Page 67: 3 clocking error interrupt mask, 4 adcx overflow interrupt mask, Cs4234

DS899F1

67

CS4234

6.22 Interrupt Mask 1 (Address 1Fh)

6.22.1

Test Mode Error Interrupt Mask

Allows or prevents a Test Mode Error event from flagging the interrupt pin. A test mode error occurs when

an inadvertent I²C write places the device in test mode.

6.22.2

Serial Port Error Interrupt Mask

Allows or prevents a Serial Port Error event from flagging the interrupt pin. A serial port error occurs when

any of the following control port parameters are changed without first placing the device into power down

(power down is defined as all

bits are set to 1):

• Serial Port Format:

• Speed Mode:

(If the MCLK/F

S

ratio changes without the device being powered

down, it will flag this error as well as the Clocking Error.)

6.22.3

Clocking Error Interrupt Mask

Allows or prevents a Clocking Error event from flagging the interrupt pin. See

for details.

6.22.4

ADCx Overflow Interrupt Mask

Allows or prevents an ADCx Overflow event from flagging the interrupt pin.

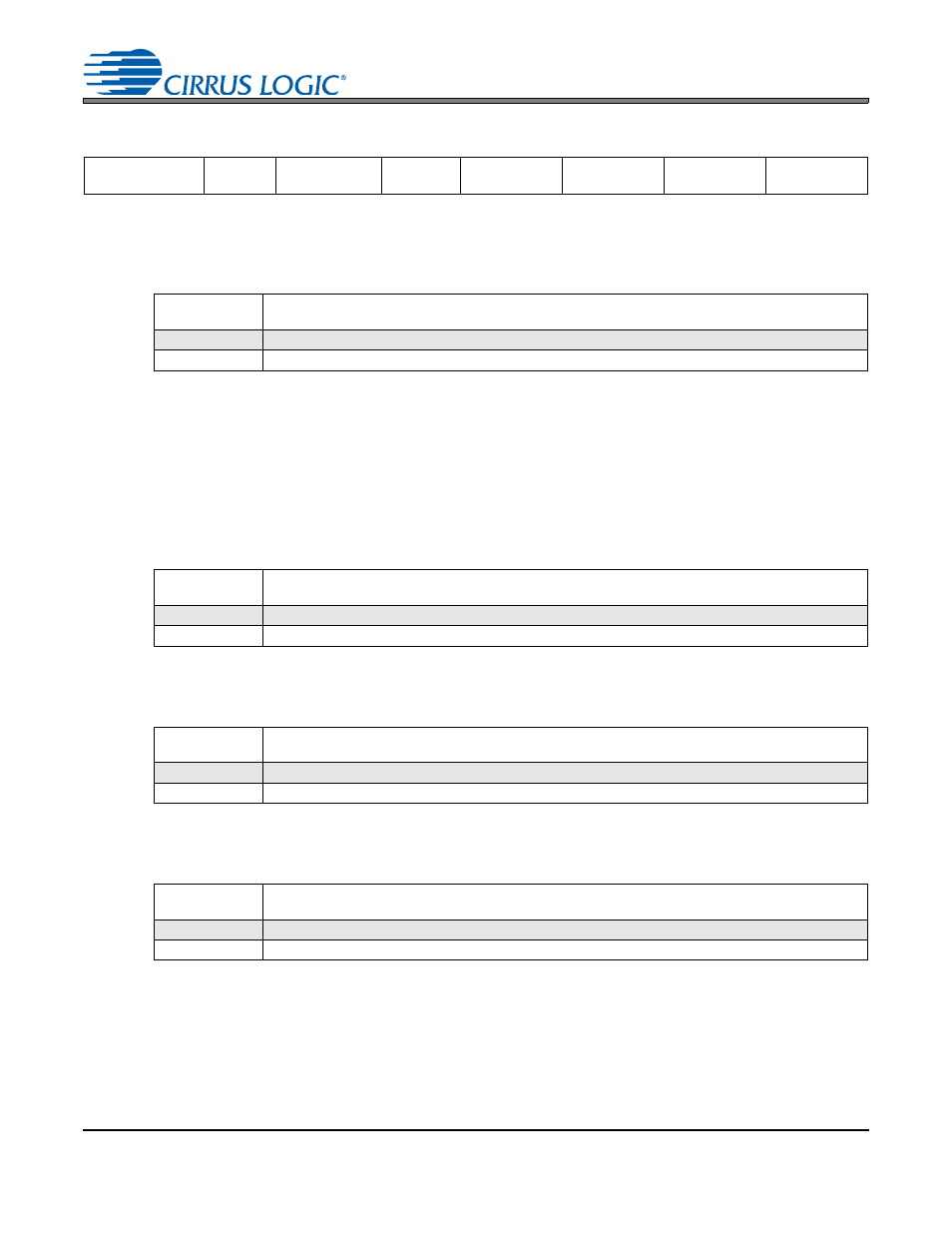

7

6

5

4

3

2

1

0

MASK

TST MODE ERR

MASK

SP ERR

MASK

CLK ERR

Reserved

MASK

ADC4 OVFL

MASK

ADC3 OVFL

MASK

ADC2 OVFL

MASK

ADC1 OVFL

MASK

TST MODE ERR

In the event of a Test Mode Error event, Interrupt Pin will:

0

Be Flagged

1

Not be flagged

MASK

SP ERR

In the event of a Serial Port Error event, Interrupt Pin will:

0

Be Flagged

1

Not be flagged

MASK

CLK ERR

In the event of a Clocking Error event, Interrupt Pin will:

0

Be Flagged

1

Not be flagged

MASK

ADCx OVFL

In the event of an ADCx Overflow event, Interrupt Pin will:

0

Be Flagged

1

Not be flagged