13 adc control 2 (address 10h), 1 mute adcx, 2 power down adcx – Cirrus Logic CS4234 User Manual

Page 61: 14 low latency path control (address 11h), 1 low latency noise gate, 2 invert low latency channel x, Khz; all, Power down adcx, Power down adcx” bits in the, Adc control 2 (address

DS899F1

61

CS4234

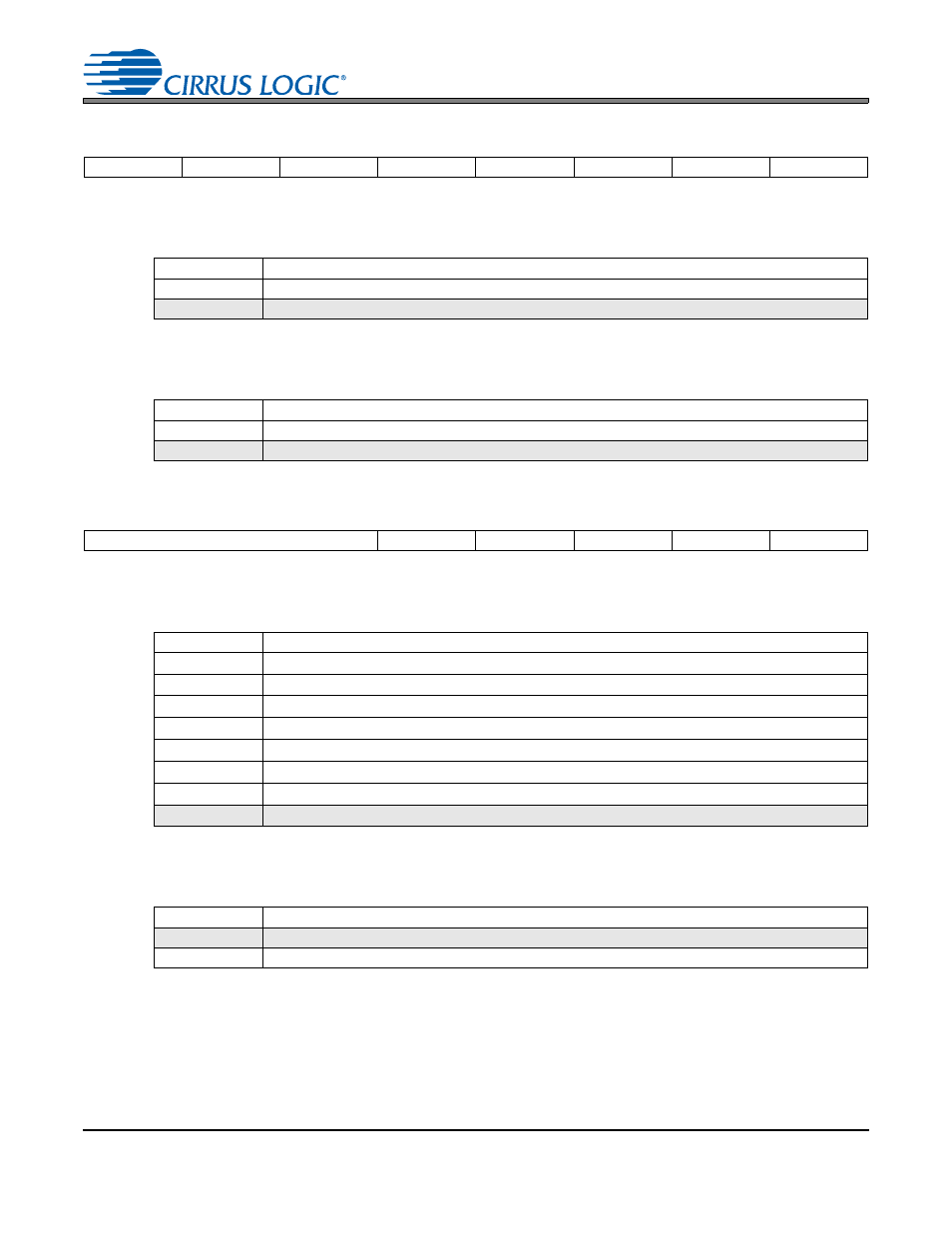

6.13 ADC Control 2 (Address 10h)

6.13.1

Mute ADCx

Mutes the ADCx signal

6.13.2

Power Down ADCx

Powers down the ADCx path.

6.14 Low Latency Path Control (Address 11h)

6.14.1

Low Latency Noise Gate

This sets the bit depth at which the Noise Gate feature should engage for the low-latency path.

6.14.2

Invert Low Latency Channel x

Inverts the polarity of the data entering into the low-latency channel.

7

6

5

4

3

2

1

0

MUTE ADC4

MUTE ADC3 MUTE_ADC2 MUTE ADC1

PDN ADC4

PDN ADC3

PDN ADC2

PDN ADC1

MUTE ADCx

ADC is:

0

Not Muted

1

Muted

PDN ADCx

ADC is:

0

Powered Up

1

Powered Down

7

6

5

4

3

2

1

0

LL NG[2:0]

Reserved

INV. LL4

INV. LL3

INV. LL2

INV. LL1

LL NG[2:0]

Noise Gate is set at: [b]

000

Upper 13 Bits (72 dB)

001

Upper 14 Bits (78 dB)

010

Upper 15 Bits (84 dB)

011

Upper 16 Bits (90 dB)

100

Upper 17 Bits (96 dB)

101

Upper 18 Bits (102 dB)

110

Upper 24 Bits (138 dB)

111

Noise Gate Disabled

INV. LLx

Low Latency Data is:

0

Not Inverted

1

INverted