4 sample width select (address 07h), 1 output sample width, 2 input sample width – Cirrus Logic CS4234 User Manual

Page 54: 3 low-latency path sample width, 4 dac5 sample width, Cs4234

DS899F1

54

CS4234

6.4

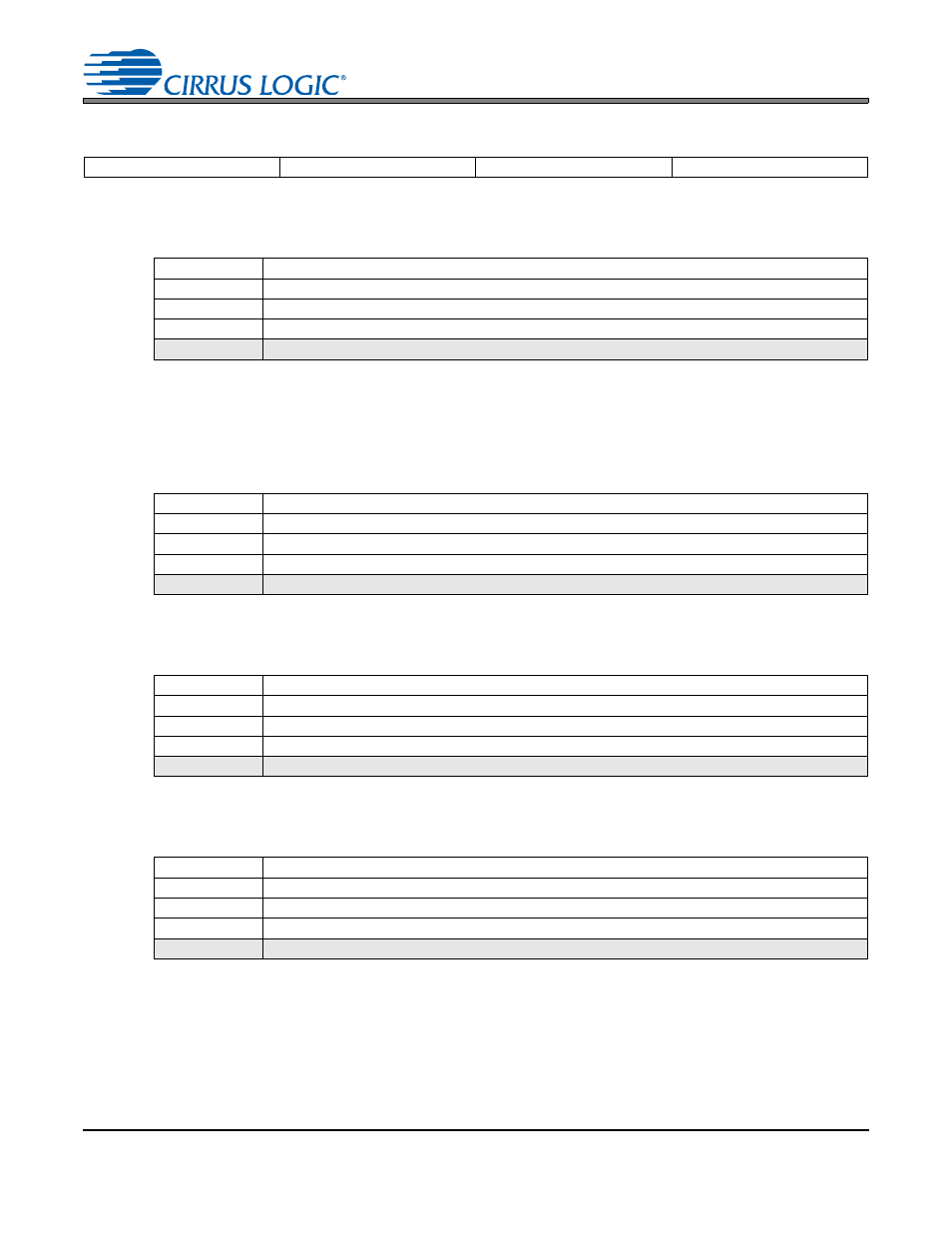

Sample Width Select (Address 07h)

6.4.1

Output Sample Width

These bits set the width of the samples placed into the outgoing SDOUTx streams.

Note:

Bits which are wider than the Output Sample Width setting above will be set to zero within the

SDOUTx data stream.

6.4.2

Input Sample Width

These bits set the width of the samples coming into the CS4234 through the SDINx TDM streams.

6.4.3

Low-Latency Path Sample Width

These bits set the width of the samples which have been placed into the low latency path of the CS4234.

6.4.4

DAC5 Sample Width

These bits set the width of the samples which have been placed into the DAC5 path of the CS4234.

7

6

5

4

3

2

1

0

SDOUTx SW[1:0]

INPUT SW[1:0]

LOW LAT. SW[1:0]

DAC5 SW[1:0]

OUTPUT SW

Sample Width is:

00

16 bits

01

18 bits

10

20 bits

11

24 bits

INPUT SW

Sample Width is:

00

16 bits

01

18 bits

10

20 bits

11

24 bits

LOW LAT. SW

Sample Width is:

00

16 bits

01

18 bits

10

20 bits

11

24 bits

DAC5 SW

Sample Width is:

00

16 bits

01

18 bits

10

20 bits

11

24 bits