Register quick reference, Va_sel, 0 for – Cirrus Logic CS4234 User Manual

Page 50: Group delay[3:0]” bits in the, Control" register, Vq ramp” bit in the, Dac control 4" register, Mclk rate[2:0]” bits in the, Clock and sp sel." register, Sdo chain” bit in the

DS899F1

50

CS4234

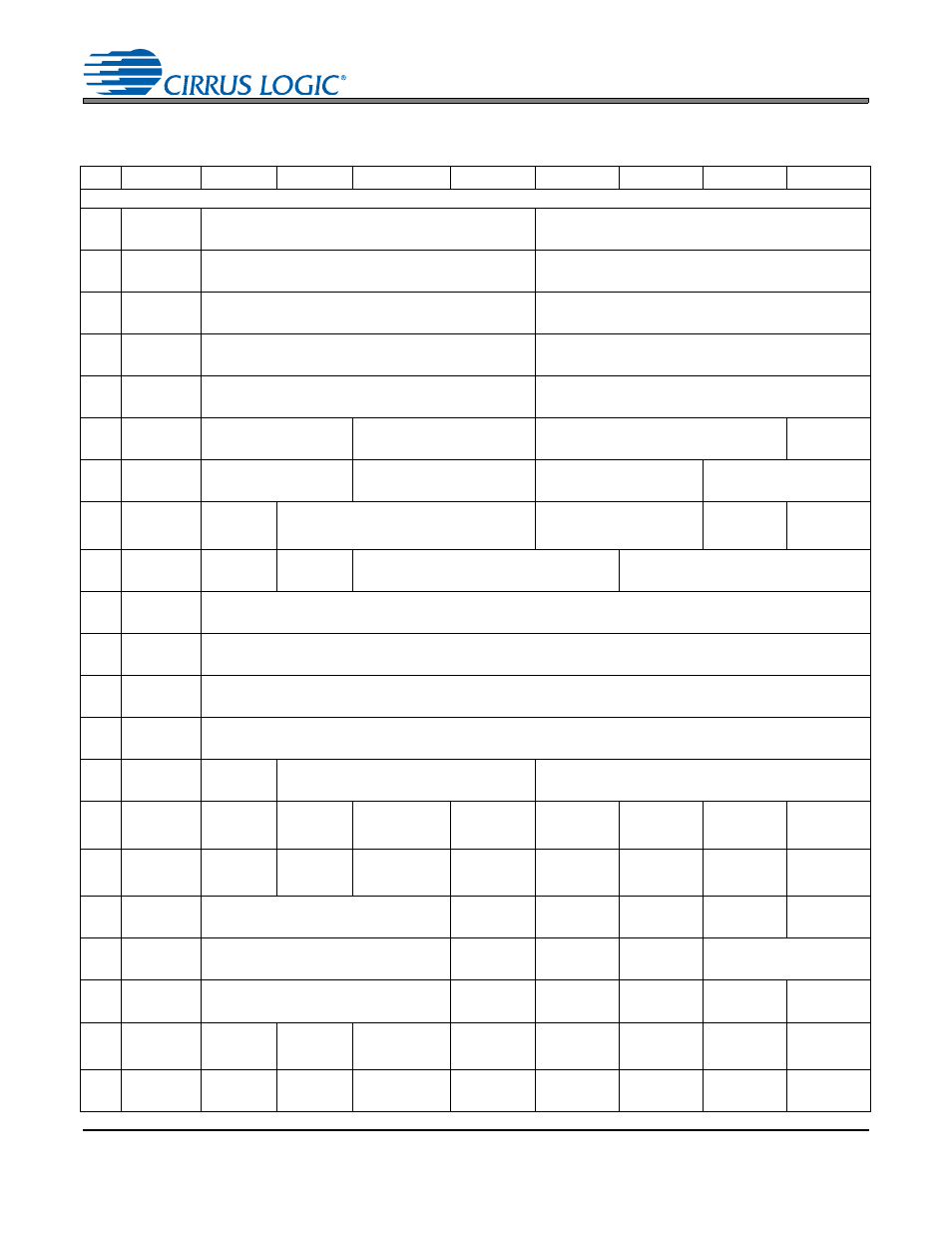

5. REGISTER QUICK REFERENCE

Default values are shown below the bit names

.

AD

Function

7

6 5 4 3 2 1 0

(Read Only Bits are shown in Italics)

01h

Device ID

A and B

DEV. ID A[3:0]

DEV. ID B[3:0]

0

1 0 0 0 0 1 0

02h

Device ID

C and D

DEV. ID C[3:0]

DEV. ID D[3:0]

0

0

1

1

0 1 0 0

03h

Device ID

E and F

DEV. ID E[3:0]

DEV. ID F[3:0]

0

0 0 0 0 0 0 0

04h

Variant ID

Reserved [3:0]

Reserved [3:0]

0

0 0 0 0 0 0 0

05h

Revision ID

ALPHA REV. ID[3:0]

NUMERIC REV. ID[3:0]

x

x

x

x

x

x

x

x

06h

Clock and

SP Sel.

BASE RATE[1:0]

SPEED MODE[1:0]

MCLK RATE[2:0]

Reserved

0

0 0 0 0 1 0 0

07h

Sample

Width Sel.

SDOUTx SW[1:0]

INPUT SW[1:0]

LOW LAT. SW[1:0]

DAC5 SW[1:0]

1

1 1 1 1 1 1 1

08h

SP Control

INV SCLK

DAC5 SOURCE[2:0]

SP FORMAT[1:0]

SDO CHAIN

MASTER/

SLAVE

0

1 0 0 1 0 0 0

09h

SP Data

Sel.

Reserved

Reserved

DAC1-4 SOURCE[2:0]

LL SOURCE[2:0]

0

0 0 0 0 0 0 1

0Ah

SDIN1

Mask 1

SDIN1 MASK 1[7:0]

1

1 1 1 1 1 1 1

0Bh

SDIN1

Mask 2

SDIN1 MASK 2[7:0]

1

1 1 1 1 1 1 1

0Ch

SDIN2

Mask 1

SDIN2 MASK 1[7:0]

1

1 1 1 1 1 1 1

0Dh

SDIN2

Mask 2

SDIN2 MASK 2[7:0]

1

1 1 1 1 1 1 1

0Eh

TPS

Control

TPS MODE

TPS OFFSET[2:0]

GROUP DELAY[3:0]

0

0 0 0 0 0 0 0

0Fh

ADC

Control 1

Reserved

Reserved

VA_SEL

ENABLE

HPF

INV. ADC4

INV. ADC3

INV. ADC2

INV. ADC1

1

1

0 0 0 0 0 0

10h

ADC

Control 2

MUTE

ADC4

MUTE

ADC3

MUTE

ADC2

MUTE

ADC1

PDN

ADC4

PDN

ADC3

PDN

ADC2

PDN

ADC1

1

1 1 1 1 1 1 1

11h

Low Lat.

Control 1

LL NG[2:0]

Reserved

INV. LL 4

INV. LL 3

INV. LL 2

INV. LL 1

1

1 1 0 0 0 0 0

12h

DAC

Control 1

DAC1-4 NG[2:0]

DAC1-4 DE

DAC5 DE

DAC5 MVC

DAC5 CFG & FLTR[1:0]

1

1 1 0 0 0 0 0

13h

DAC

Control 2

DAC5 NG[2:0]

INV. DAC5

INV. DAC4

INV. DAC3

INV. DAC2

INV. DAC1

1

1 1 0 0 0 0 0

14h

DAC

Control 3

DAC5 ATT.

DAC1-4

ATT.

MUTE

LL

MUTE

DAC5 MUTE

DAC4 MUTE

DAC3 MUTE

DAC2 MUTE

DAC1

1

0 1 1 1 1 1 1

15h

DAC

Control 4

VQ RAMP

TPS GAIN

Reserved

PDN DAC5

PDN DAC4 PDN

DAC3 PDN

DAC2 PDN

DAC1

0

0 0 1 1 1 1 1