34921a d-sub connectors, Bank 1 bank 2, Low frequency multiplexer switch modules – Agilent Technologies Switch/Measure User Manual

Page 117

Low Frequency Multiplexer Switch Modules

4

34980A User’s Guide

105

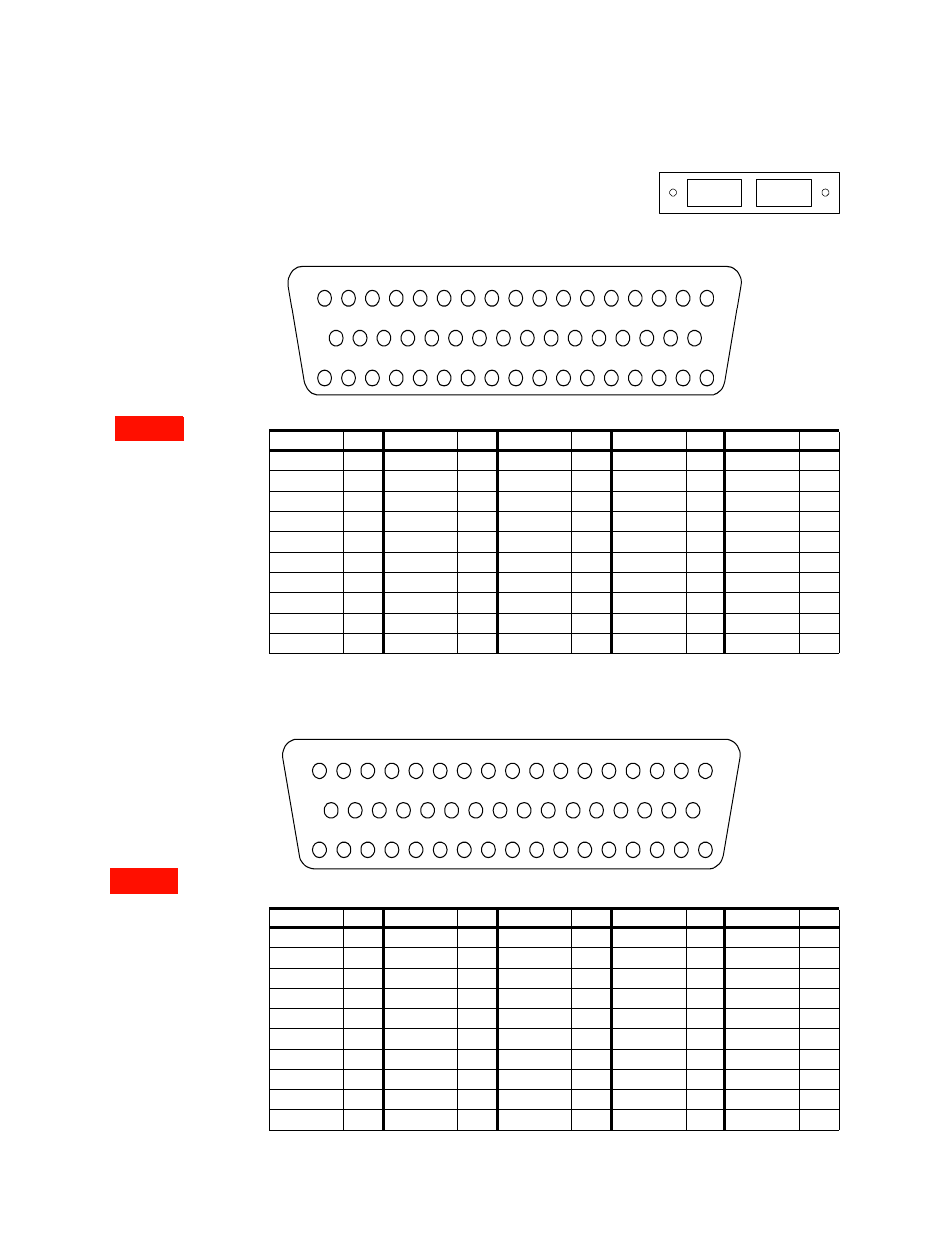

34921A D-Sub Connectors

Bank 1

Bank 2

For orientation, the D-sub connector

end of the module is facing you.

Bank 2

Bank 1

17L

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

TSIL* 11H

11L

7H

7L

17H

13H

13L

9H

9L

19H

19L

15H 15L Interlock 1

Interlock1

1H

1L

2H

2L

3H

3L

COM

1H

COM

1L

4H

4L

14H

14L

5H

5L

20H

20L

18H

GND

6H

6L

16H

16L 12H

12L

8H

8L

18L

10H

10L

AMP

41L

AMP

41

I

AMP

42L

AMP

42

I

*TSIL represents

Temperature Sensor

Interface Line. This line

is used for temperature

interface only.

Description Pin

Description Pin

Description Pin

Description Pin

Description Pin

1H

1

6H

35

11H

19

16H

37

COM1 H

7

1L

2

6L

36

11L

20

16L

38

COM1 L

8

2H

3

7H

21

12H

39

17H

23

Interlock 1

17

2L

4

7L

22

12L

40

17L

24

Interlock 1

33

3H

5

8H

41

13H

25

18H

43

GND

34

3L

6

8L

42

13L

26

18L

44

TSIL*

18

4H

9

9H

27

14H

11

19H

29

AMP 41L

47

4L

10

9L

28

14L

12

19L

30

AMP 41

I

48

5H

13

10H

45

15H

31

20H

15

AMP 42L

49

5L

14

10L

46

15L

32

20L

16

AMP 42

I

50

WARNING::

As a safety

feature, interlock 1 pins

(17 and 33) on Bank 1

must be shorted to

enable the Bank 1 Analog

Bus relays to close. The

optional 34921T terminal

block shorts these pins

for you. This feature

protects inadvertent

routing of high voltages

from the Analog Bus to

the D-sub connector of

the module.

WARNING

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

23L

Interlock 2

21H

21L

22H

22L 23H

COM

2H

COM

2L

24H

24L 34H

34L

25H

25L

40H

40L

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

37L

TSIL* 31H

31L

27H

27L 37H

33H

33L

29H

29L

39H

39L

35H 35L Interlock 2

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

GND

26H

26L 36H

36L 32H

32L

28H

28L 38H

38L

30H 30L

AMP

43L

AMP

43

I

AMP

44L

AMP

44

I

*TSIL represents

Temperature Sensor

Interface Line. This line

is used for temperature

interface only.

Description

Pin

Description

Pin

Description

Pin

Description

Pin

Description

Pin

21H

1

26H

35

31H

19

36H

37

COM2 H

7

21L

2

26L

36

31L

20

36L

38

COM2 L

8

22H

3

27H

21

32H

39

37H

23

Interlock 2

17

22L

4

27L

22

32L

40

37L

24

Interlock 2

33

23H

5

28H

41

33H

25

38H

43

GND

34

23L

6

28L

42

33L

26

38L

44

TSIL*

18

24H

9

29H

27

34H

11

39H

29

AMP 43L

47

24L

10

29L

28

34L

12

39L

30

AMP 43

I

48

25H

13

30H

45

35H

31

40H

15

AMP 44L

49

25L

14

30L

46

35L

32

40L

16

AMP 44

I

50

WARNING::

As a safety

feature, interlock 2 pins

(17 and 33) on Bank 2

must be shorted to

enable the Bank 2 Analog

Bus relays to close. The

optional 34921T terminal

block shorts these pins

for you. This feature

protects inadvertent

routing of high voltages

from the Analog Bus to

the D-sub connector of

the module.

WARNING