AltiGen comm ACM 5.1 User Manual

Page 146

Chapter 11: Board Configuration

132

AltiWare ACM 5.1 Administration Manual

Note:

For ideally synchronized systems, Transmit and Receive Frame Slips

counters should be ‘0.’ Continuous update of the frame slips counters means

that transmit and receive frequencies are not equal. In this case, you should

check the system and CT-Bus clock setup.

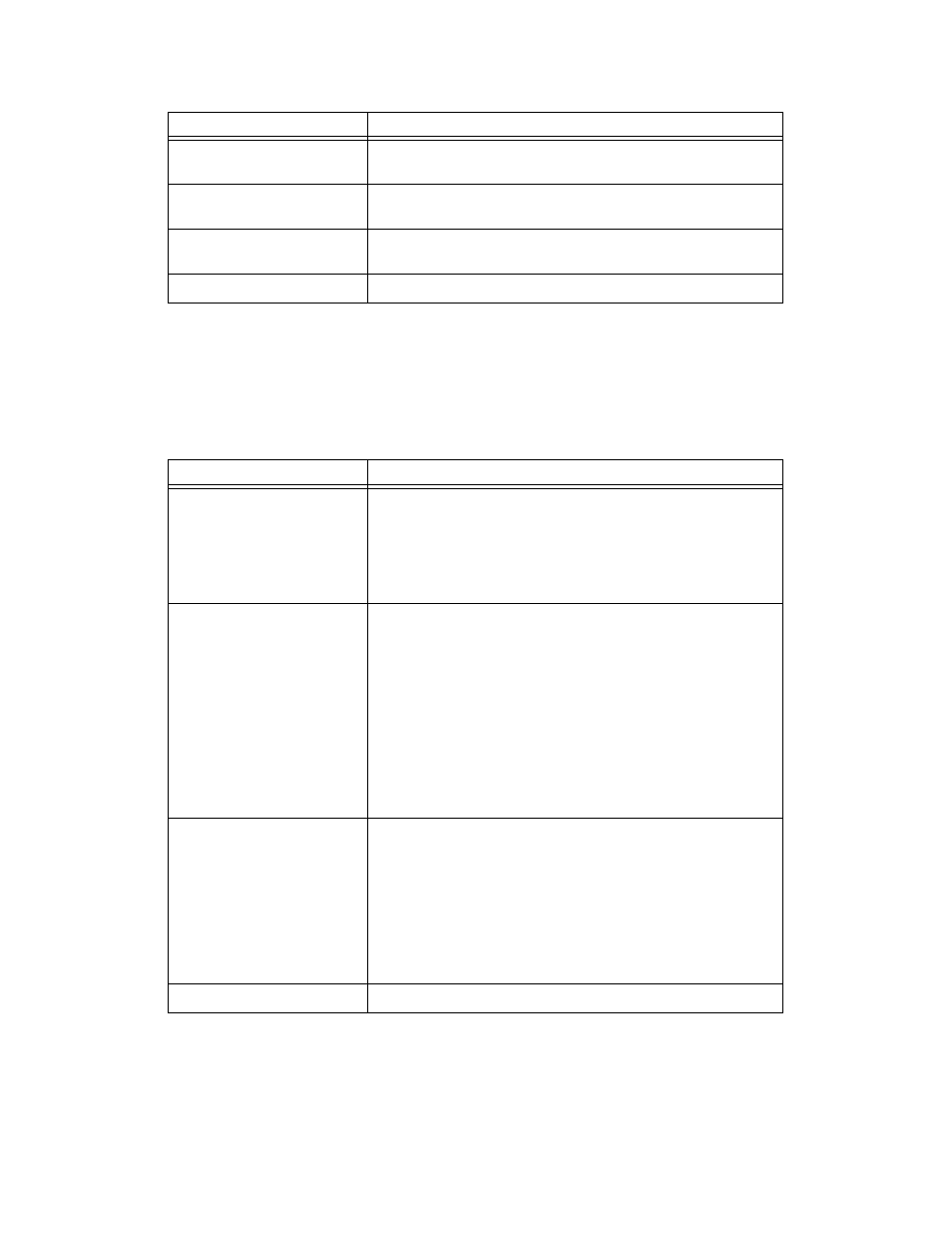

Setting the Configurable Options

These are the options you can set:

Line Code Errors

Line Code Error is defined as an occurrence of a bi-polar

variation or excessive zeroes.

Bit Errors

Bit Errors are defined as a CRC-6 error in ESF, FT-bit

error in SLC-96 and F-bit or sync bit error in SF.

Xmt Frame Slips

Transmit Frame Slips counter shows the number of

frame slips for the transmitter

Clear button

Use the Clear button to reset the statistics counters.

Option

Notes

Frame Type

•

For T1, you can set the Frame Type to either SF or ESF.

SF (Superframe Format) consists of 12 consecutive

frames. ESF (Extended Superframe Format) consists of

24 consecutive frames.

•

For E1, you can set the Frame Type to either No CRC or

CRC4. CRC4 is embedded into 16 consecutive frames.

Line Code

•

For T1, you can set the Line Code to either AMI or

B8ZS. AMI (Alternate Mark Inversion) is the line coding

format in T1 transmission systems whereby successive

ones (marks) are alternately inverted and sent with

opposite polarity of the preceding mark. B8ZS (Binary 8

Zero Substitution) sends two violations of the bipolar line

encoding technique, rather than inserting a one for every

seven consecutive zeros.

•

For E1, you can set the Line Code to either AMI or

HDB3. HDB3 (High Density Bipolar Order) is based on

AMI, but extends this by inserting violation codes

whenever there is a run of four or more zeros.

Zero Code Suppression

You can set the Zero Code Suppression to None (default

setting), Jam Bit 8, GTE or Bell.

Zero Code Suppression inserts a “one” bit to prevent the

transmission of eight or more consecutive “zero” bits; Jam

Bit 8 forces every bit 8 to a one; GTE Zero Code

Suppression replaces bit 8 of an all zero channel byte to a

one, except in signaling frames where bit 7 is forced to a

one. Bell Zero Code Suppression replaces bit 7 of an all zero

channel byte with a one.

CD Bits Handling

CD Bits Handling is not editable.

Error

Meaning