Figure 3-20. status reporting structure, 20 status reporting structure -61 – KEPCO BOP 1KW-MG Operator Manual, Firmware Ver.2.38 to 2.47 User Manual

Page 125

BOP HIPWR 080709

3-61

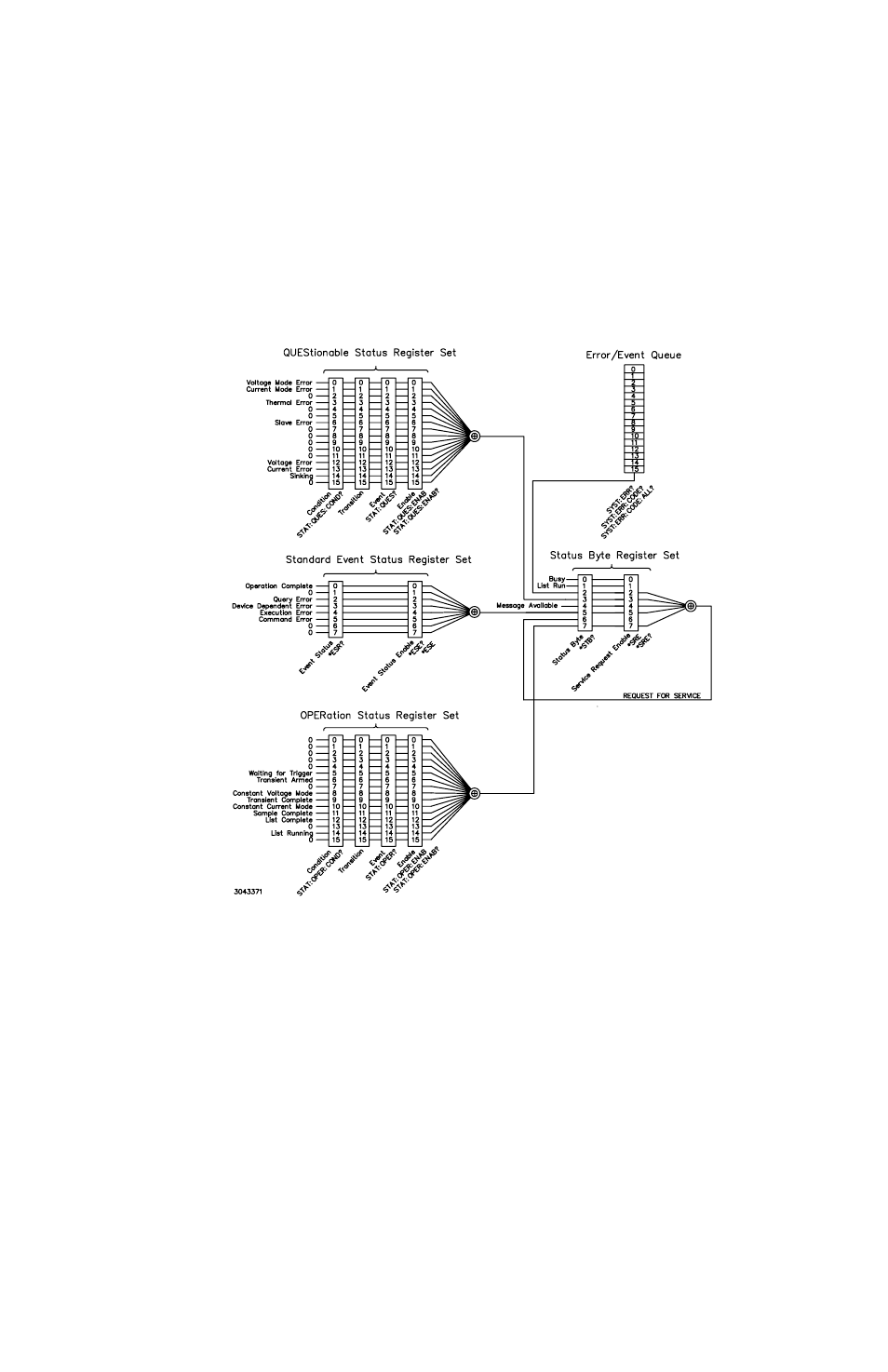

FIGURE 3-20. STATUS REPORTING STRUCTURE

A zero to one transition of a condition register is added to the event register. Reading an event

register clears all of the bits found in the event register. If any bits are set in an event register,

the following condition register bit is then set. For example, if the STAT:QUES:ENB (enable) reg-

ister has bit 0 set and a voltage error is detected, the event registers bit 0 is set. The 1 in the

event register causes bit 3 of the status byte to be asserted. The Service Request register is

ANDed with its enable register for all bits except bit 6. The result is placed in bit 6 of the Service

Request register. If bit 6 is a 1 (true), it causes the MBT-G power supply to assert the SRQ line

to the host controller.

- ABC-DM SERIES (96 pages)

- ATE (all models) QUICK START GUIDE (8 pages)

- SN 488-D (16 pages)

- SN 488-D (94 pages)

- SN 488-D (14 pages)

- BHK-MG 200W (Full Rack) Series (152 pages)

- BHK-MG 40W (Half Rack) Series (148 pages)

- BIT 232 (72 pages)

- BIT 4882 (56 pages)

- BIT 4886 Quick Start Guide (4 pages)

- BIT 4886 Operator Manual (92 pages)

- BOP 100W, 200W, 400W (M, D) Quick Start Guide (8 pages)

- BOP 20-5ML Modification Sheet (1 page)

- BOP 20-10MC Modification Sheet (2 pages)

- BOP 36-6MC Modification Sheet (2 pages)

- BOP 100-2MC Modification Sheet (2 pages)

- BOP 50-4MC Modification Sheet (2 pages)

- BOP 100-2ML Modification Sheet (2 pages)

- BOP 72-3ML Modification Sheet (2 pages)

- BOP 50-4ML Modification Sheet (2 pages)

- BOP 36-6ML Modification Sheet (2 pages)

- BOP 20-10ML Modification Sheet (2 pages)

- BOP 72-6MC Modification Sheet (2 pages)

- BOP 36-12MC Modification Sheet (2 pages)

- BOP 20-20MC Modification Sheet (2 pages)

- BOP 100-4ML Modification Sheet (2 pages)

- BOP 72-6ML Modification Sheet (2 pages)

- BOP 50-8ML Modification Sheet (2 pages)

- BOP 36-12ML Modification Sheet (2 pages)

- BOP 20-20ML Modification Sheet (2 pages)

- BOP 1KW-MG Quick Start Guide (16 pages)

- BOP 1KW-MG Quick Reference Guide (2 pages)

- BOP 1KW-MG Operator Manual, Firmware Ver.4.12 and higher (196 pages)

- BOP 1KW-MG Operator Manual, Firmware Ver.4.08 to 4.11 (194 pages)

- BOP 1KW-MG Operator Manual, Firmware Ver.3.05 to 4.07 (194 pages)

- BOP 1KW-MG Operator Manual, Firmware Ver.2.48 to 3.04 (188 pages)

- BOP 1KW-MG Operator Manual, Firmware Ver.2.01 to 2.37 (176 pages)

- BOP 1KW as Solar Device Tester Quick Start Guide (3 pages)

- BOP-GL 1KW Quick Start Guide (16 pages)

- BOP-GL 1KW Operator Manual Firmware Ver.3.05 and higher (168 pages)

- BOP-HV (48 pages)

- CA 26 (2 pages)

- CA 27 (2 pages)

- CA 29 (2 pages)