Telex Integrated Signal Processor ISP-100 User Manual

Page 58

7-6

10 July 1998

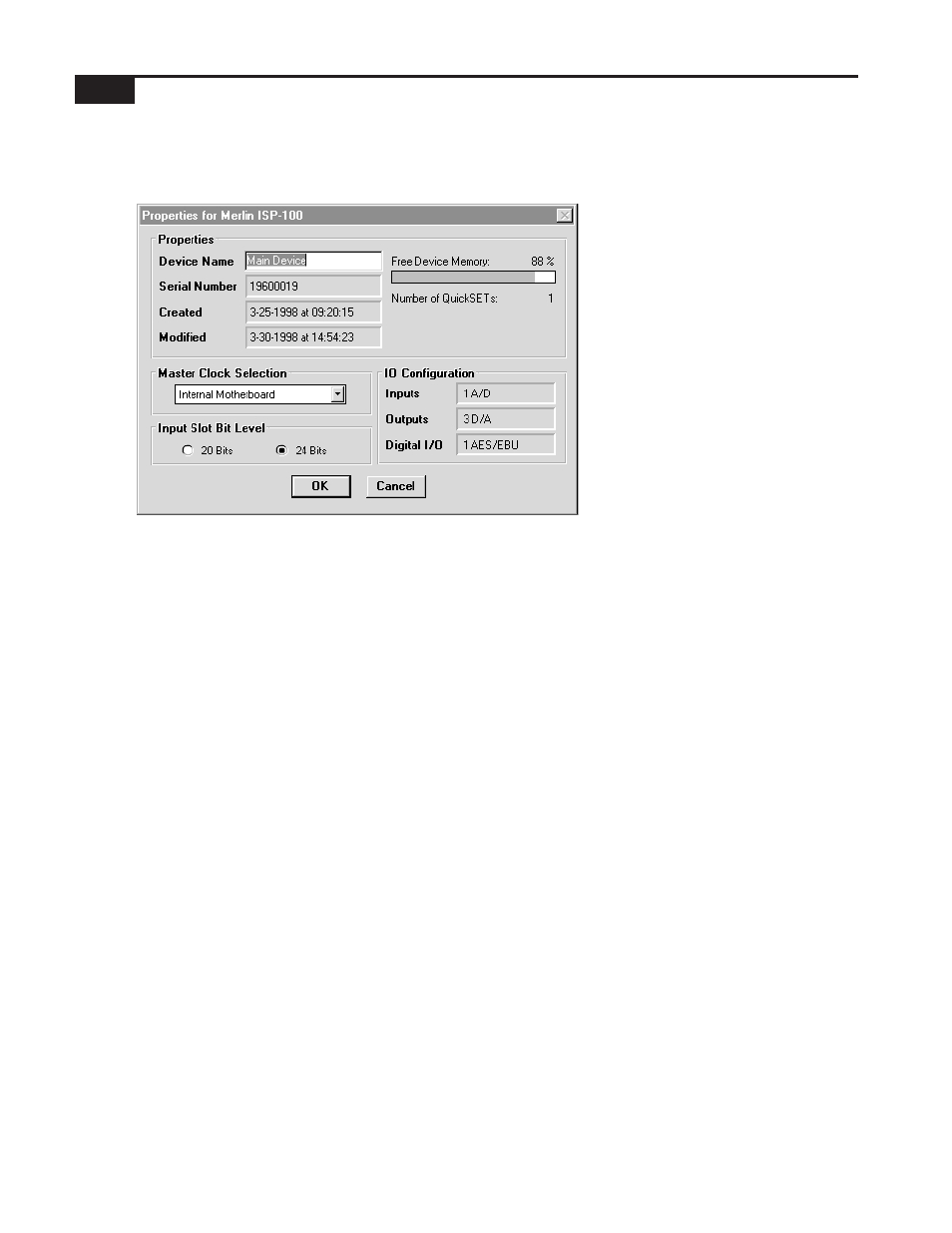

able to access ISP-100 statistics such as free memory, number of

QuickSETs, etc.

Properties for the ISP-100

Figure 7-10 ISP-100 properties dialog.

Properties for the ISP-100 (see Figure 7-10) reports statistics on the

ISP-100. It is accessed by double clicking on the entry next to the

star icon (see Figure 7-9), or by clicking on the entry next to the star

icon (see Figure 7-9) and then clicking on the Properties button in the

Project Manager.

Master Clock Selection

There are four location selections for master clock:

1. Main Board – no reference frequency. (default).

2. Slot #1 – 12.288 MHz reference frequency (AES/EBU only).

3. Slot #2 – 12.288 MHz reference frequency (AES/EBU only).

4. External Reference – 12.288, 6.144, or 3.072 MHz via

external input BNC.

An error will be returned if either slot 1 or slot 2 is selected as the

clock master while the slot contains a card configured to use the

sample rate converter (SRC).

The default clock master is the main board. If the user places an

AES/EBU card in an input slot the user can manually change the

clock master to select either the main, external sync, or input

card slot.

Input Slot Bit Level

The input slot bit level can be set to either 20-bit or 24-bit. 20-bit is

usually associated with consumer grade (SPDIF) digital audio.

24-bit is usually associated with professional grade (AES/EBU)

digital audio. However, it is possible to have consumer grade 24-

bit digital audio. For optimal performance be sure to set the proper

bit level for the audio data stream.