Reference clock pulse width register, Serial prom update register, Version register – Motorola ATCA-717 User Manual

Page 147: Table, Aaaaaa, Lower divider register, Upper divider register, Section "version register" on

FPGA Registers

Maps and Registers

PENT/ATCA−717

147

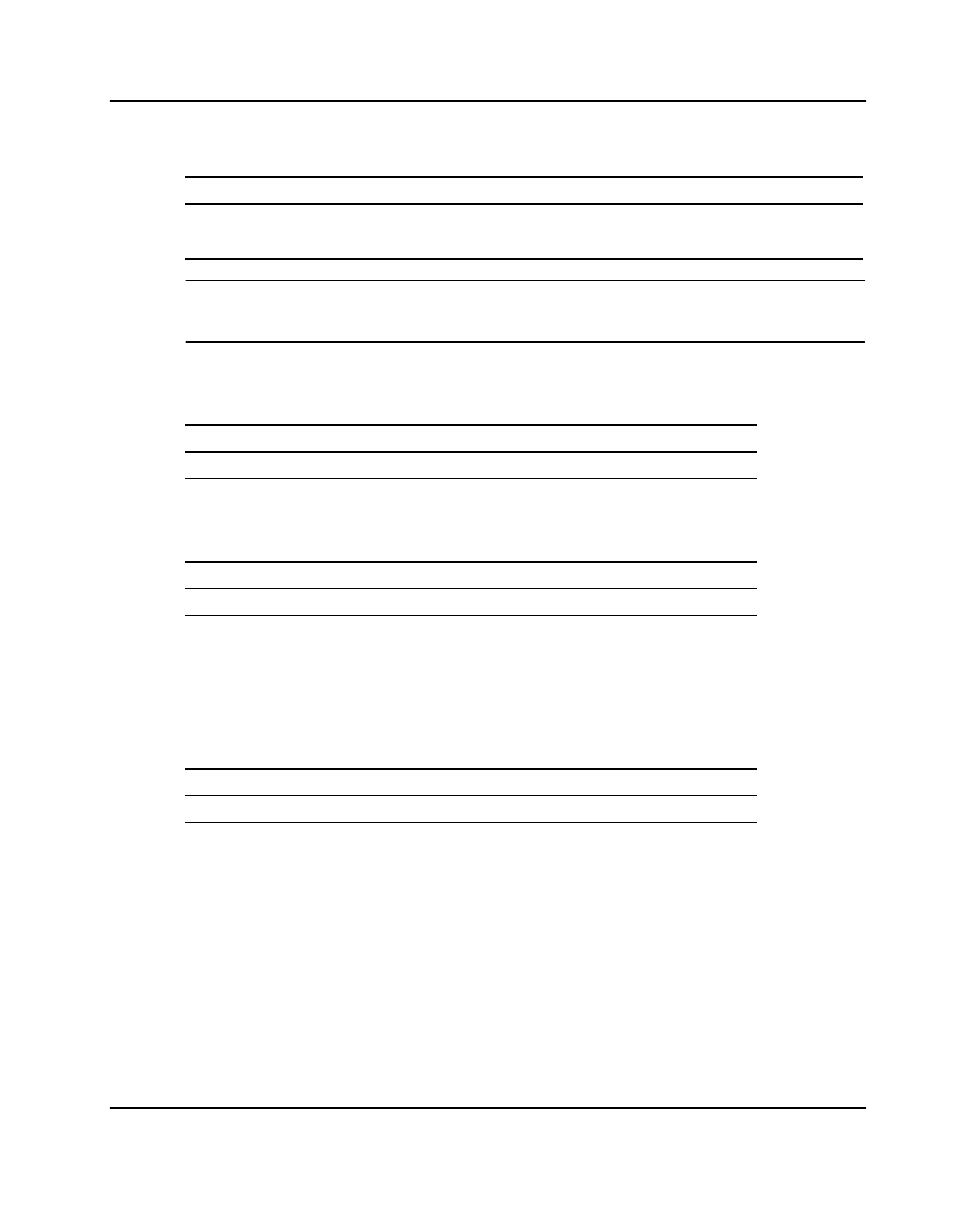

Recovered Clock Frequency

Division Factor

Reference Clock Frequency

38.88 MHz

19.44 MHz

2

77.76 MHz

19.44 MHz

4

Note:

a

If the division factor is 1, i.e. no clock division is done, the clock divider should

be bypassed. This can be done via the reference clock source register.

a

Lower Divider Register

Table 32:

Lower Divider Register

Bit

Description

Default

Access

7..0

Divider lower byte

01

16

r/w

Upper Divider Register

Table 33:

Upper Divider Register

Bit

Description

Default

Access

7..0

Divider upper byte

00

16

r/w

Reference Clock Pulse Width Register

This register determines the width of the reference clock high pulse in numbers of

recovered clock cycles. The minimum pulse width is 150ns. If the clock divider is

bypassed or the reference clock frequency is not 8 kHz, no pulse is generated.

a

Table 34:

Reference Clock Pulse Width Register

Bit

Description

Default

Access

7..0

Pulse width of reference clock signal

01

16

r/w

Serial PROM Update Register

The FPGA image is stored in two redundant PROMS.This register is used by upper layer

software to control the upgrade of the FPGA image. Consult your local Motorola

representative for the availability of new FPGA image versions and upgrade software.

a

Version Register

This register indicates the version of the FPGA. The initial value is FE

16

a

and is counted

down with each new release.

a