5 timing closure issues, 2 general timing closure issues, Timing closure issues – BECKHOFF ET1100 User Manual

Page 30: General timing closure issues

EtherCAT IP Core for Altera FPGAs

26

Slave Controller

– Application Note FAQ

4.2.5

Timing closure issues

4.2.5.1

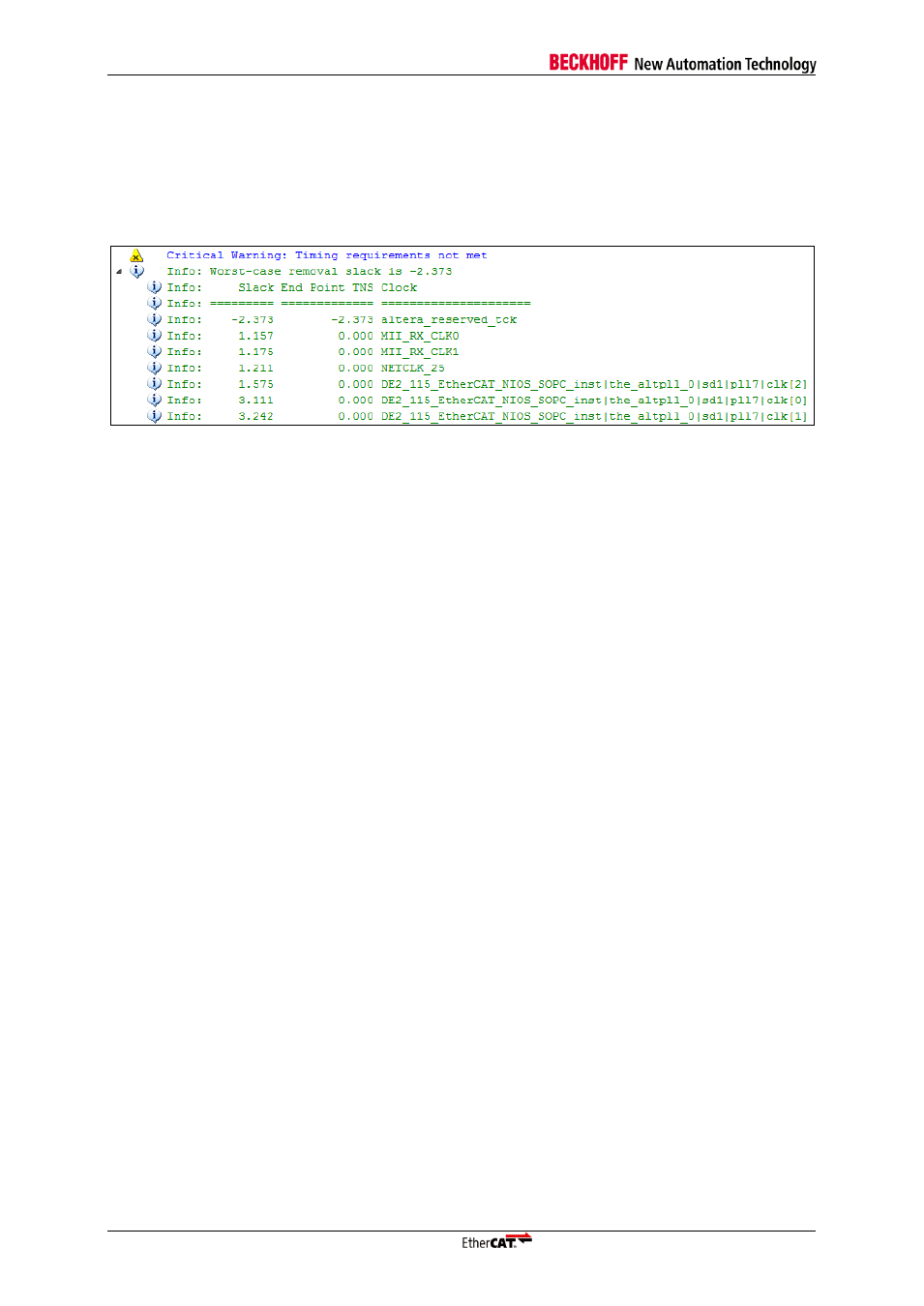

OpenCore Plus logic does not achieve timing (altera_reserved_tck)

Sometimes timing requirements are not met with OpenCore Plus. Experience shows that timing

violations related to the clock altera_reserved_tck can be ignored. They do not occur with the full

version.

Figure 10: Timing requirement of OpenCore Plus logic not met

4.2.5.2

General timing closure issues

Regarding constraints, we can only give general advice on increasing the synthesis effort. The default

synthesis and implementation features are a good starting point, the following additional options might

increase timing closure:

Analysis & Synthesis Settings

Optimization Technique = Area

Timing-Driven Synthesis = On

Advanced:

Auto Resource Sharing = Off

Remove Duplicate Registers = Off

Compilation Process Settings

– Physical Synthesis Optimizations – Optimize for

performance (physical synthesis)

Perform physical synthesis for combinational logic = On

Perform register retiming = On

Effort level = Normal (or even Extra)

Fitter Settings

Fitter effort = Standard

General advice

Over-constraining was not found useful with current synthesis, it might cause the tools to put too much

effort in paths which would originally pass, and consequently making other paths slower.

Find out if the violating path consists basically of logic or routing delays. If the logic delays are too

high, reduce the number of features, increase optimization effort, or use a faster speed grade.

Generally, the more features are used, the tighter becomes the timing. Especially 64 bit Distributed

Clocks are very demanding, due to the high register count. The low-cost FPGAs are often not able to

use 64 bit DC at all. In many cases using 32 bit DC solves the problem.

If many FPGA resources are available, the design is sometimes spread widely across the FPGA,

resulting in long connections with high routing delay. Reduce the available FPGA resources/area for

the EtherCAT IP Core to improve timing.

Generally, it is impossible to predict timing closure for custom user logic in combination with all IP

Core configurations and FPGA devices. Final certainty can only be reached by implementing the

design

– that is what the evaluation versions are for. There will be combinations which are not able to

reach timing closure at all.