4 error counter interpretation guide, Error counter interpretation guide – BECKHOFF ET1100 User Manual

Page 12

General Issues

8

Slave Controller

– Application Note FAQ

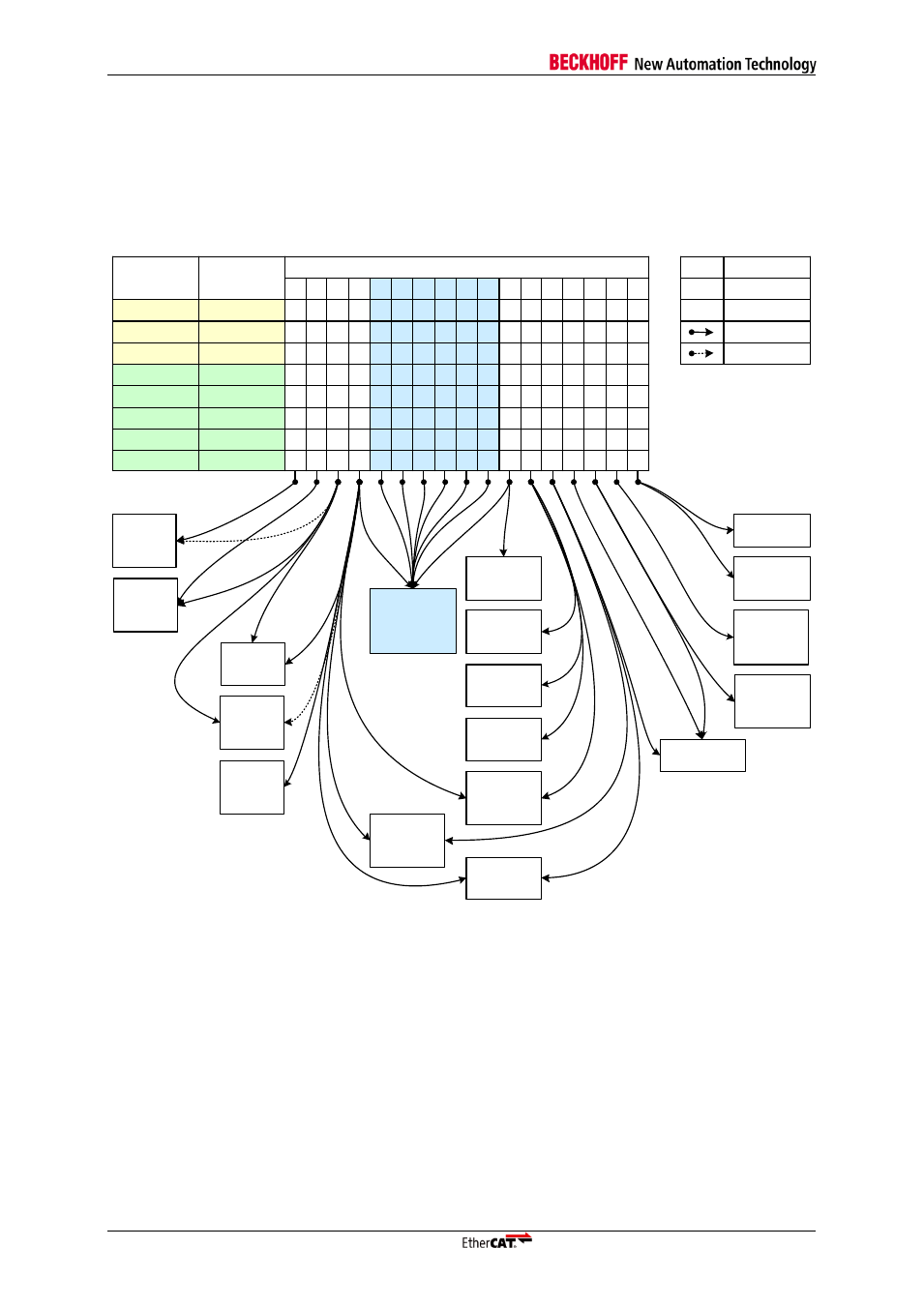

3.12.4 Error counter interpretation guide

The following diagram can be used to identify possible error causes. At first, find out which error

counters are increasing in your network (or device), and at the master. Compare this with each of the

cases shown in the main table of Figure 2 and find the most similar case. Follow the arrows at the

bottom of each column to the possible error causes. Use Table 1 for comments and error localization.

Phantom

frames (power

up/enh. Link

det.)

Subsequent

fault

Non-EtherCAT

frame

<64 byte/>2KB

Too long frame

> 2KB

Too short

frame

< 64 Byte

Physical layer

issue

(PHY-to-PHY,

EBUS-to-EBUS)

Clock

deviation/jitter

(quartz/PLL

issue)

Cable dis-

connected,

link partner

powered down

MII issue

(ESC-to-PHY,

timing)

Port 0 closed

automatically

at 2 or more

slaves

Master violates

EtherCAT

frame structure

TX_ER floating

FPGA internal

timing issue

Lost frame

TwinCAT RX Err

TwinCAT TX Err

ESC CRC Err

ESC RX Err

ESC Forw. Err.

ESC EPU Err.

ESC Lost link

Master

Master

Master

0x0300 (+2/4/6)

0x0301 (+2/4/6)

0x0308 (+1/2/3)

0x030C

0x0310 (+1/2/3)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

+

+ +

--

--

--

--

--

+ +

+

+ +

(+)

+

+

+

(+)

(+)

(+)

+

+

+

(+)

(+)

+

(+)

(+)

+

+

(+)

(+)

+

(+)

+

(+)

(+)

(+)

(+)

(+)

(+)

Master too

slow

(TX FIFO

underrun)

IFG too

short

(dropped

frame)

Open port

into nirwana

(no link)

Non-

EtherCAT

frame

(dropped)

17

+

--

(+)

Increasing

Might be increasing/

available

No data / no

communication

+

+

PHYs

reduce

preamble

length*

*Refer to AN PHY

selection guide

Common cause

Unusual cause

Register

Error counter

Cases

Figure 2: Error counters interpretation guide