Zilog Z8F0130 User Manual

Page 75

eZ8

™

CPU Core

User Manual

UM012820-0810

eZ8

™

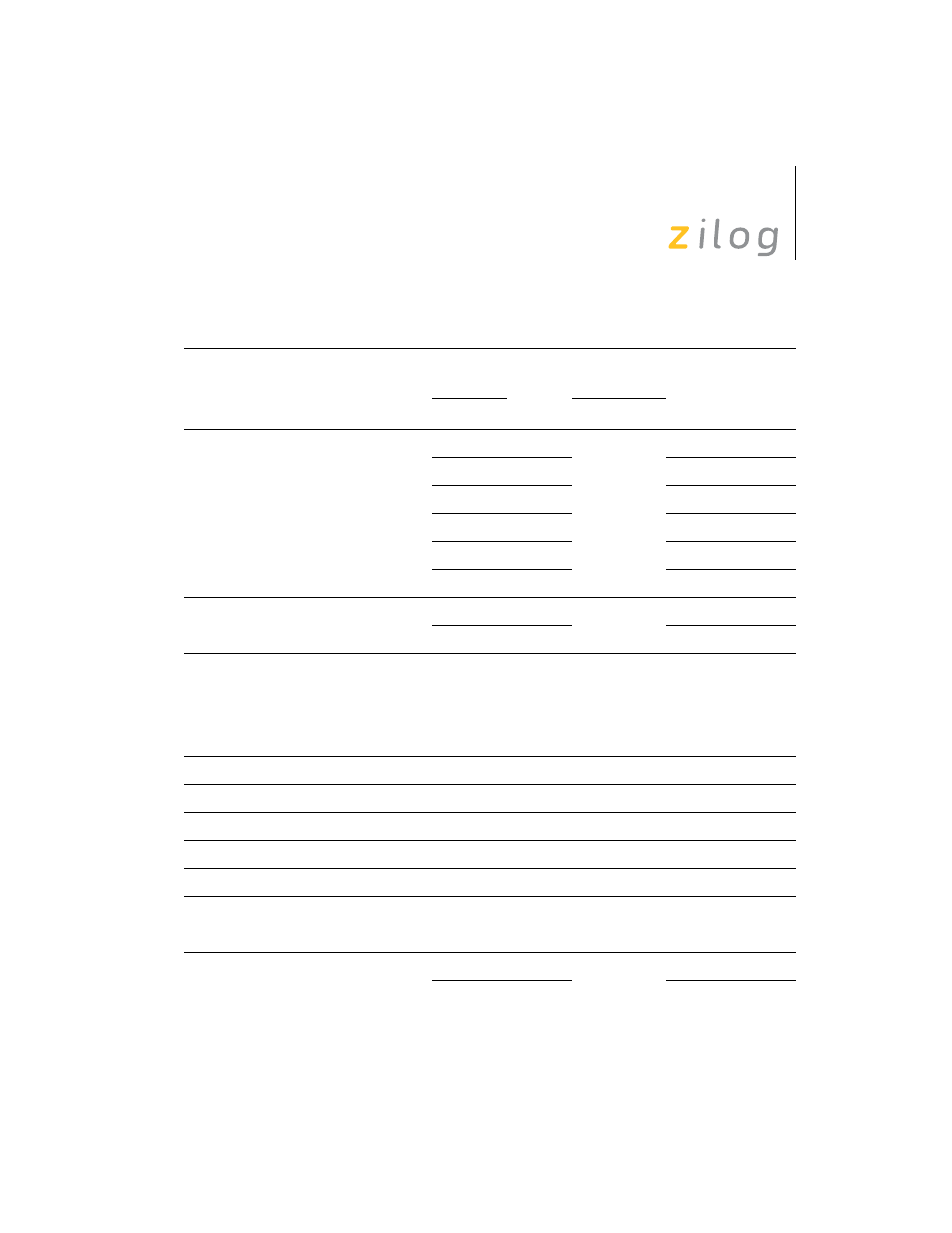

CPU Instruction Set Summary

60

AND dst, src dst

dst AND src

r

r

52

– * * 0 – –

2

3

r

Ir

53

2

4

R

R

54

3

3

R

IR

55

3

4

R

IM

56

3

3

IR

IM

57

3

4

ANDX dst,

src

dst

dst AND src

ER

ER

58

– * * 0 – –

4

3

ER

IM

59

4

3

ATM

Block all interrupt

and DMA requests

during execution of

the next 3

instructions

2F

– – – – – –

1

2

BCLR bit, dst dst[bit]

0

r

E2

– – – – – –

2

2

BIT p, bit, dst dst[bit]

p

r

E2

– – – – – –

2

2

BRK

Debugger Break

00

– – – – – –

1

2

BSET bit, dst dst[bit]

1

r

E2

– – – – – –

2

2

BSWAP dst

dst[7:0]

dst[0:7]

R

D5

X * * 0 – –

2

2

BTJ p, bit,

src, dst

if src[bit] = p

PC

PC + X

r

F6

– – – – – –

3

3

Ir

F7

3

4

BTJNZ bit,

src, dst

if src[bit] = 1

PC

PC + X

r

F6

– – – – – –

3

3

Ir

F7

3

4

Table 20. eZ8 CPU Instruction Summary (Continued)

Assembly

Mnemonic

Symbolic

Operation

Address

Mode

Op

Code(s)

(Hex)

Flags

Fetch

Cycles

Instr.

Cycles

dst src

C Z S V D H

- Z8F0131 Z8F0230 Z8F0231 Z8F0430 Z8F0431 Z8F043A Z8F0830 Z8F0831 Z8F083A Z8F1232 Z8F1233 Z8F0113 Z8F011A Z8F0123 Z8F012A Z8F0213 Z8F021A Z8F0223 Z8F022A Z8F0411 Z8F0412 Z8F0413 Z8F041A Z8F0421 Z8F0422 Z8F0423 Z8F042A Z8F0811 Z8F0812 Z8F0813 Z8F081A Z8F0821 Z8F0822 Z8F0823 Z8F082A Z8F0880 Z8F1621 Z8F1622 Z8F1680 Z8F1681 Z8F1682 Z8F2421 Z8F2422 Z8F2480 Z8F3221 Z8F3222 Z8F3281 Z8F3282 Z8F4821 Z8F4822 Z8F4823 Z8F6081 Z8F6082 Z8F6421 Z8F6422 Z8F6423 Z8F6481 Z8F6482 Z8FS021A ZMOT1AHH Z8FS040B ZMOT0BHH ZMOT0BSB Z8FMC04 Z8FMC08 Z8FMC16