Zilog Z8F0130 User Manual

Page 36

eZ8

™

CPU Core

User Manual

UM012820-0810

Address Space

21

Because Working Registers can be specified using fewer operand bytes,

there are fewer bytes of code needed, which reduces execution time. In

addition, when processing interrupts or changing tasks, the Register

Pointer speeds context switching. The Set Register Pointer (SRP)

instruction sets the contents of the Register Pointer.

16-Bit Register Pairs

Register data may be accessed as a 16-bit word using Register Pairs. In

this case, the most significant byte (MSB) of the data is stored in the even

numbered register, while the least significant byte (LSB) is stored in the

next higher odd numbered register (see

on page 22). Address the

register pair using the address of the MSB.

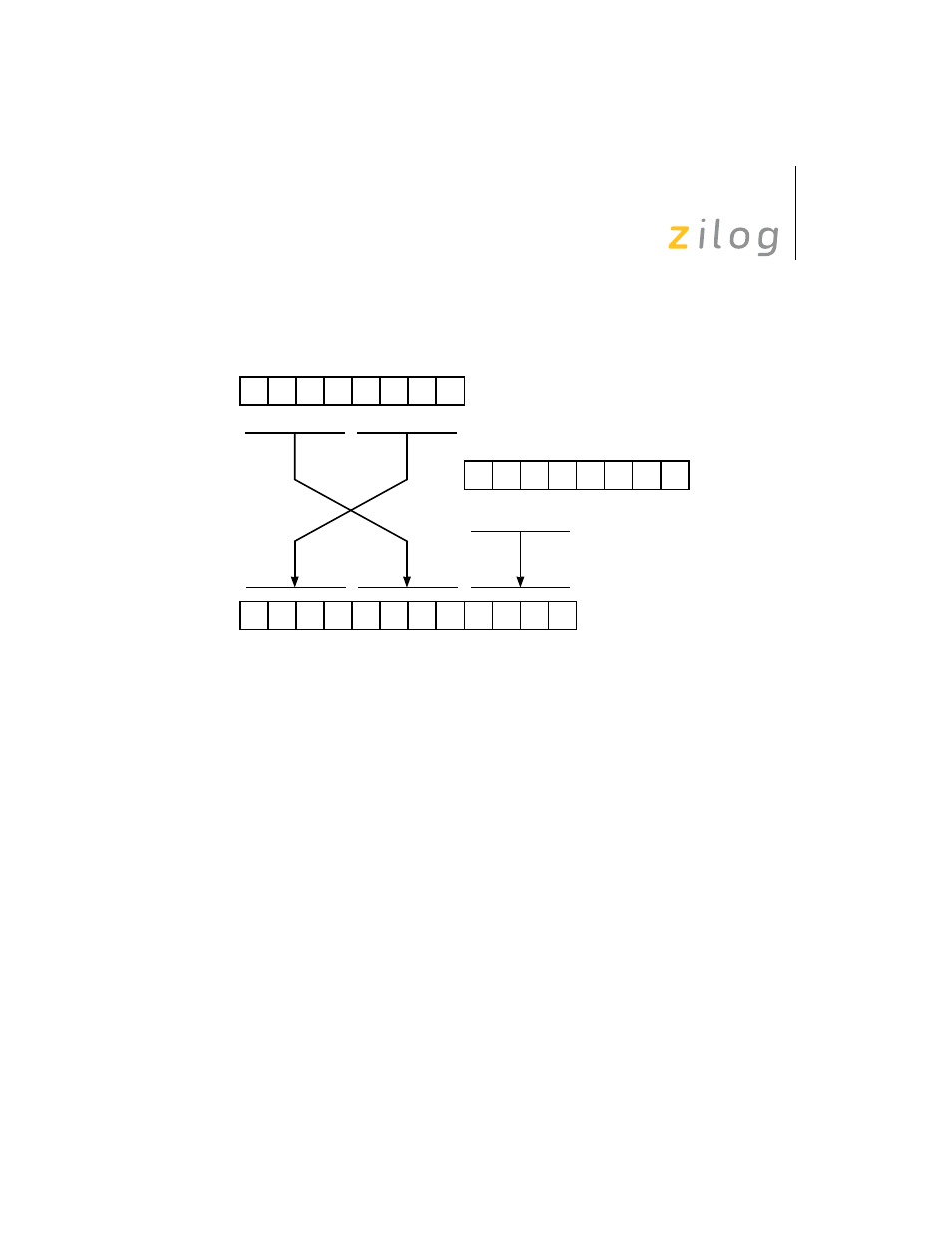

Figure 4. Working Register Addressing Example

0

1

1

1

0

0

1

1

Register Pointer

0

1

1

0

1

1

1

0

INC R6

0

1

1

1

0

1

1

0

Bit

0

Bit

7

0

0

1

1

Full 12-bit Register Address (376h)

Bit

11

Bit

0

Working Group

Page

Working Register

4-bit Address

- Z8F0131 Z8F0230 Z8F0231 Z8F0430 Z8F0431 Z8F043A Z8F0830 Z8F0831 Z8F083A Z8F1232 Z8F1233 Z8F0113 Z8F011A Z8F0123 Z8F012A Z8F0213 Z8F021A Z8F0223 Z8F022A Z8F0411 Z8F0412 Z8F0413 Z8F041A Z8F0421 Z8F0422 Z8F0423 Z8F042A Z8F0811 Z8F0812 Z8F0813 Z8F081A Z8F0821 Z8F0822 Z8F0823 Z8F082A Z8F0880 Z8F1621 Z8F1622 Z8F1680 Z8F1681 Z8F1682 Z8F2421 Z8F2422 Z8F2480 Z8F3221 Z8F3222 Z8F3281 Z8F3282 Z8F4821 Z8F4822 Z8F4823 Z8F6081 Z8F6082 Z8F6421 Z8F6422 Z8F6423 Z8F6481 Z8F6482 Z8FS021A ZMOT1AHH Z8FS040B ZMOT0BHH ZMOT0BSB Z8FMC04 Z8FMC08 Z8FMC16