Signal naming convention –30, Signal naming convention – Altera POS-PHY Level 2 and 3 Compiler User Manual

Page 58

3–30

Chapter 3: Functional Description

Interface Signals

POS-PHY Level 2 and 3 Compiler User Guide

© November 2009

Altera Corporation

Preliminary

Figure 3–19

shows the timing of the Atlantic interface with a master source.

Signal Naming Convention

When you include an Atlantic interface in a design, the IP Toolbench generates the

signal names, which are prefixed by

b2_ena

, b2_val.

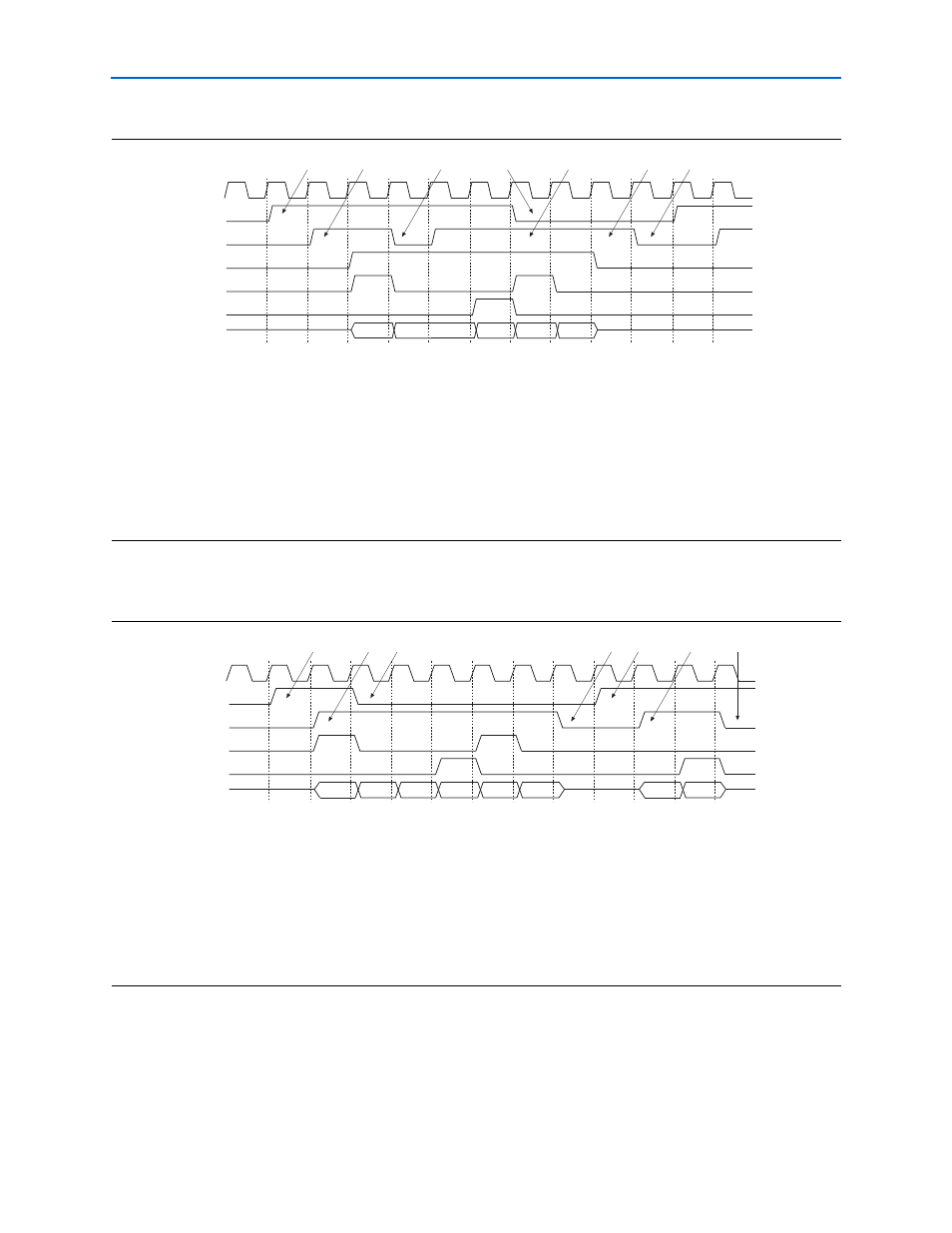

Figure 3–18. Atlantic Interface Timing—Slave Source to Master Sink

Notes to

Figure 3–18

:

(1) Slave source indicates that data is available (either threshold words available, or EOP).

(2) Master sink begins reading data.

(3) Master sink decides to stop reading the data for one clock cycle. val remains asserted and data, sop, and eop hold their current

values.

(4)

Slave source indicates that it has less than threshold

words available. The master sink can continue to read data until it detects val

deasserted.

(5) Master sink continues to read data, validates data with val.

(6) Slave source cannot supply any more data, so deasserts val.

(7) Master sink goes idle until dav is re-asserted.

clk

dav

ena

val

sop

eop

dat

(1)

(2)

(3)

(4)

(5)

(6)

(7)

Figure 3–19. Atlantic Interface Timing—Master Source to Slave Sink

Notes to

Figure 3–19

:

(1)

Slave sink indicates it has space for at least threshold

words.

(2) The master source begins writing data to the slave sink.

(3)

Slave sink indicates it has space for threshold

words. Master source can continue to send data, but must ensure that the slave sink does

not overflow.

(4) Master source stops sending data

(5)

Slave sink indicates it has space for at least threshold

words.

(6) Master source begins writing data to the slave sink.

(7) Slave sink indicates it still has space, but the master source has run out of data.

clk

dav

ena

sop

eop

dat

(1)

(2)

(3)

(5)

(4)

(6)

(7)