Interface signals, Base address –16 sx always –16, Interface signals –16 – Altera POS-PHY Level 2 and 3 Compiler User Manual

Page 44

3–16

Chapter 3: Functional Description

Interface Signals

POS-PHY Level 2 and 3 Compiler User Guide

© November 2009

Altera Corporation

Preliminary

Direct (No Addressing) mode does not include address matching or bus tri-stating

(currently not supported).

Base Address

Base address is only supported in POS-PHY level 2 mode. It configures the base

address of the POS-PHY port. For a single channel interface (‘A’ or ‘B’), the interface

responds to only the configured base address. For a multi-channel interface (‘A’ only),

the interface responds to addresses between base address and base address + number

of ‘B’ interfaces.

SX Always

SX always is only valid for POS-PHY level 3 link transmit (multi-channel) or PHY

receive (source) interfaces. You can set the SX output behavior to one of the following

conditions:

■

Normal—generates an SX cycle only when changing channels

■

Always—an SX cycle is generated for every burst and at the end of packets

1

For POS-PHY level 3 sink interfaces, the MegaCore function supports either behavior

transparently.

Interface Signals

The following section describes the interface signals for the MegaCore functions.

Figure 3–15

shows the input/output specification.

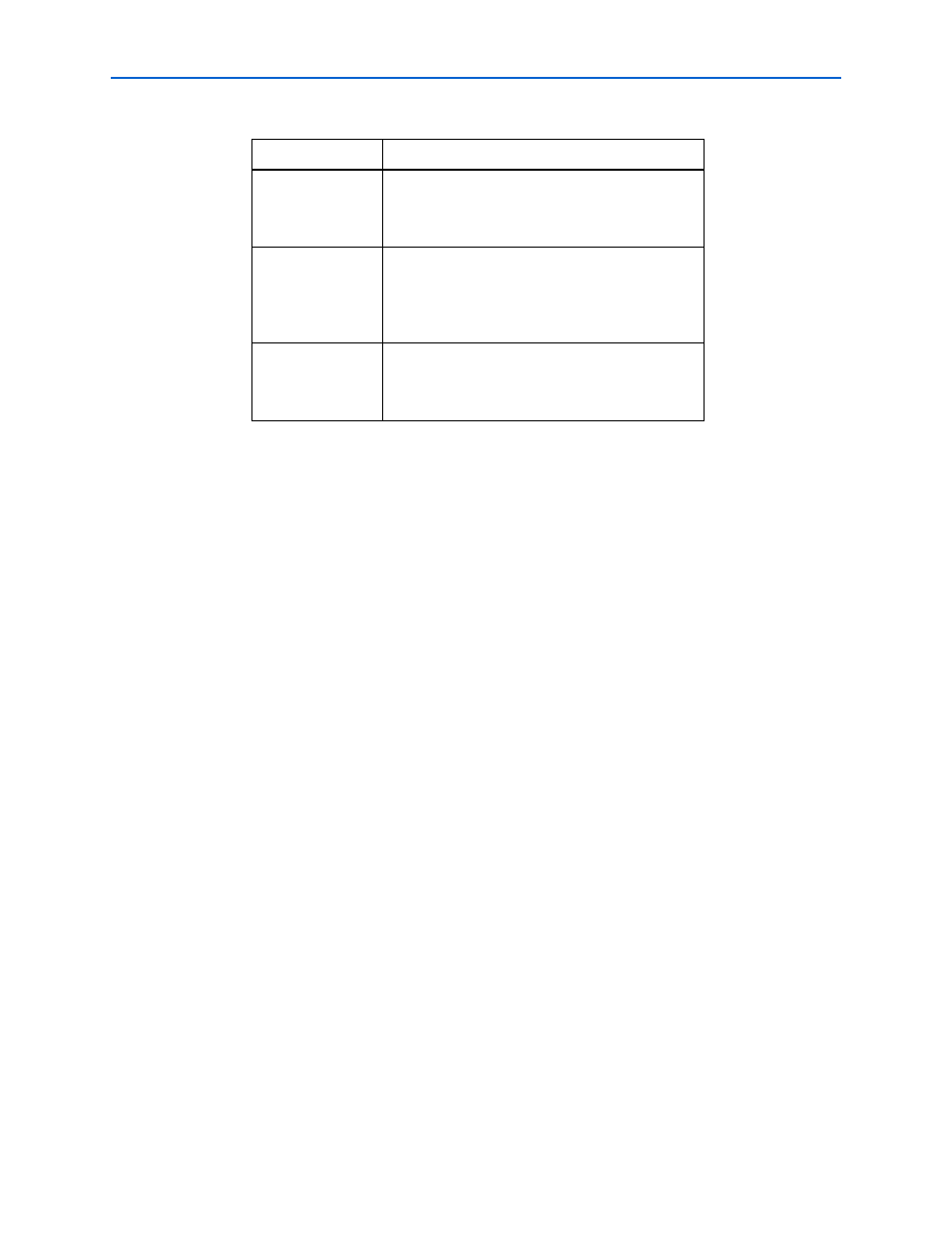

Table 3–7. Multi- & Single-Channel Packet Available Mode Options (POS-PHY Level 2)

Option

Description

Direct

In the POS-PHY transmit direction the MegaCore

function uses one dtpa pin per supported channel.

In the POS-PHY receive direction the MegaCore

function uses one drpa pin per supported channel.

Polled

In the POS-PHY transmit direction the MegaCore

function uses tadr, ptpa, and stpa to support all

channels. In the POS-PHY receive direction the

MegaCore function uses radr and prpa to support

all channels.

Polled (Ignore

stpa

)

In the POS-PHY transmit direction the MegaCore

function uses tadr and ptpa pins to support all

channels. The stpa signal is removed from the

MegaCore function.