Global interface, Pos-phy level 3 interface, Global interface –17 pos-phy level 3 interface –17 – Altera POS-PHY Level 2 and 3 Compiler User Manual

Page 45

Chapter 3: Functional Description

3–17

Interface Signals

© November 2009

Altera Corporation

POS-PHY Level 2 and 3 Compiler User Guide

Preliminary

Global Interface

Table 3–8

describes the global interface signals.

The ‘A’ interface and each ‘B’ interface have independent resets, which are provided

to allow you to assert the reset asynchronously to its clock domain. They are not

intended to provide individual channel resets. If one channel needs a reset, all

channels must be reset. Deasserting the resets must be done synchronously to its clock

domain.

Additionally, IP Toolbench can connect the independent resets and clocks to a

common reset and clock (see

‘A’ interface signals are prefixed by a_; ‘B’ interface signals are prefixed by b1_, b2_,

and so on.

POS-PHY Level 3 Interface

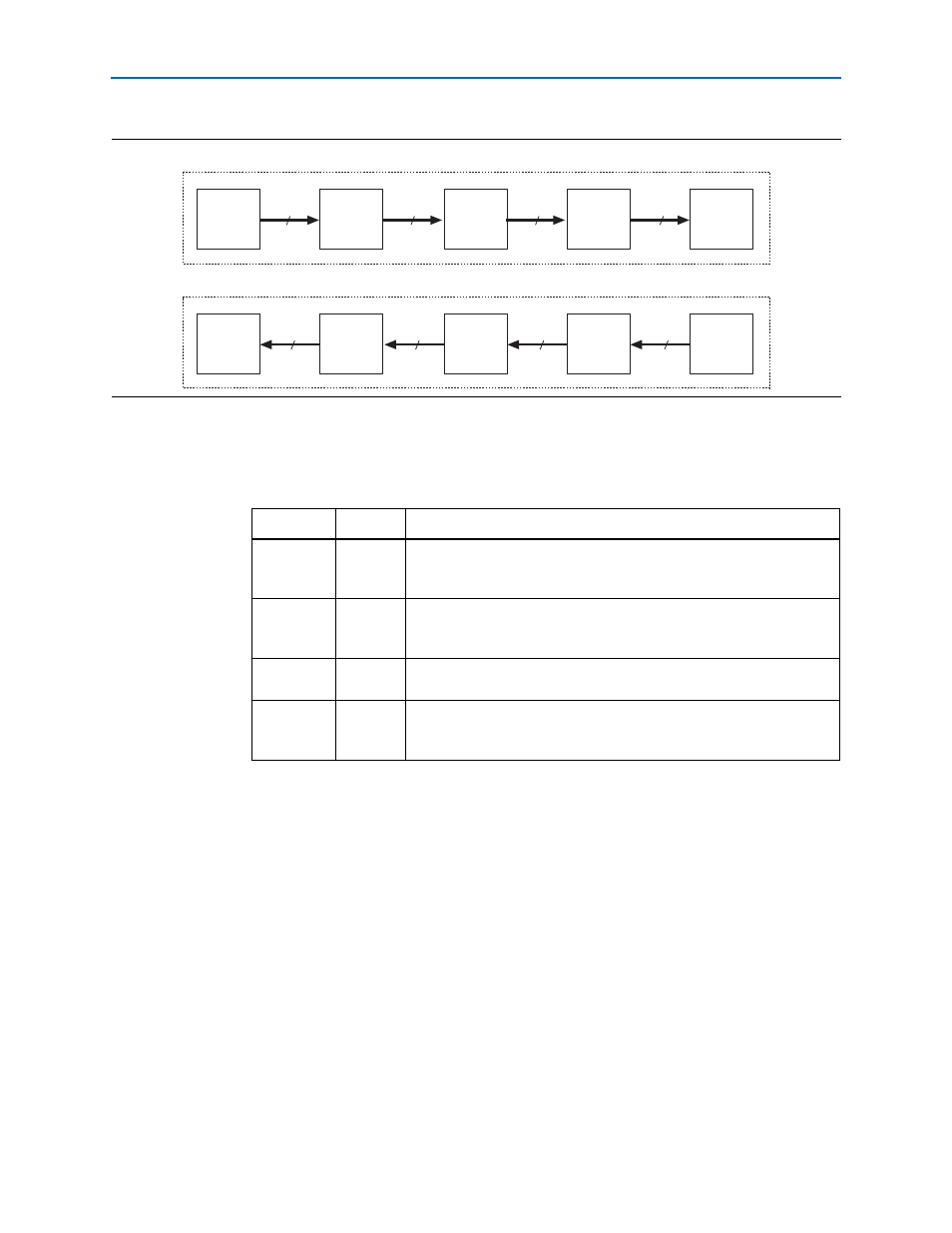

The interface direction is shown as either link to PHY, or PHY to link.

For a POS-PHY level 3 link-layer MegaCore function, the following rules apply:

Figure 3–15. Input/Output Specification

8 to 64

8 to 64

8 to 64

8 to 32

'A'

Source

Interface

Bus Width

Conversion

(wider)

8 to 64 bit

FIFO

'B'

Interface

Bus Width

Conversion

(narrower)

Source MegaCore Function

8 to 64

8 to 64

8 to 64

8 to 32

'A'

Sink

Interface

Bus Width

Conversion

(wider)

8 to 64 bit

FIFO

'B'

Interface

Bus Width

Conversion

(narrower)

Sink MegaCore Function

Table 3–8. Global Interface Description

Signal

Direction

Description

treset_n

Input

Asynchronous reset for all flip-flops on the POS-PHY source tfclk

clock domain, active low. Can be asserted asynchronously, but must be

deasserted synchronously to tfclk.

rreset_n

Input

Asynchronous reset for all flip-flops on the POS-PHY receive rfclk

clock domain, active low. Can be asserted asynchronously, but must be

deasserted synchronously to rfclk.

reset_n

Input

Asynchronous reset for the Atlantic interface, active low. Can be asserted

asynchronously, but must be deasserted synchronously to clk.

clk

Input

Clock, rising-edge active. The Atlantic interface uses single-edge

clocking. All signals are synchronous to clk, and master and slave are

in the same clock domain.

Note to

Table 3–8

:

(1) POS-PHY clock signals are described in the relevant interface tables.