Altera Cyclone II PowerPlay Early Power Estimator User Manual

Page 41

Altera Corporation

3–25

May 2006

PowerPlay Early Power Estimator User Guide For Cyclone II FPGAs

Using the Cyclone II PowerPlay Early Power Estimator

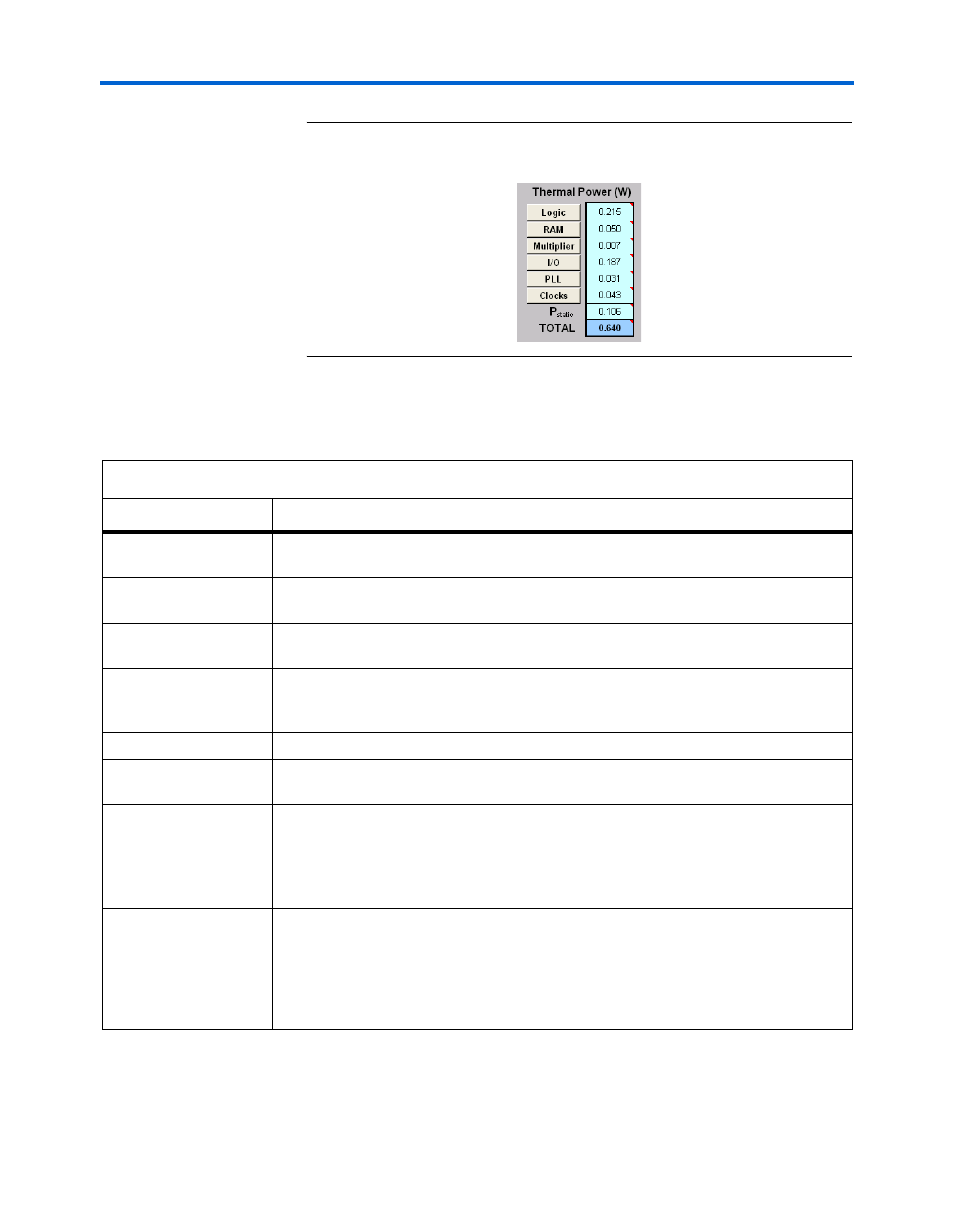

Figure 3–21. Thermal Power in the PowerPlay Early Power Estimator

Spreadsheet

Table 3–9

describes the thermal power parameters in the PowerPlay Early

Power Estimator spreadsheet.

Table 3–9. Thermal Power Section Information

Column Heading

Description

Logic

This shows the dynamic power consumed by LUTs and associated routing. Click

Logic to see details.

RAM

This shows the dynamic power consumed by RAMs blocks and associated routing.

Click RAM to see details.

Multiplier

This shows the dynamic power consumed by embedded multiplier blocks and

associated routing. Click Multiplier to see details.

I/O

This shows the dynamic power consumed by I/O pins and associated routing. Also

includes static power dissipated in terminated I/O standards on chip. Click I/O to see

details.

PLL

This shows the dynamic power consumed by PLLs. Click PLL to see details.

Clocks

This shows the dynamic power consumed by clock networks. Click Clocks to see

details.

P

s t a t i c

This shows the static power consumed irrespective of clock frequency. Does not

include static I/O current due to termination resistors, which is included in the I/O

power above.

P

s t a t i c

is affected by junction temperature, selected device, and power characteristics.

TOTAL

This shows the total power dissipated as heat from the FPGA. Does not include power

dissipated in off-chip termination resistors.

See Power Supply Current for current draw from the FPGA supply rails. This may differ

due to currents supplied to off-chip components and thus not dissipated as heat in the

FPGA.