Phase-locked loops – Altera Cyclone II PowerPlay Early Power Estimator User Manual

Page 36

3–20

Altera

Corporation

PowerPlay Early Power Estimator User Guide For Cyclone II FPGAs

May 2006

PowerPlay Early Power Estimator Spreadsheet Inputs

Phase-Locked Loops

Cyclone II devices feature fast Phase-Locked Loops (PLLs).

Each row in the PLL section represents one or more PLLs in the device.

You need to enter the maximum output frequency and the VCO

frequency for each PLL.

describes the values that need to be

entered in the PLL section of the PowerPlay Early Power Estimator

spreadsheet.

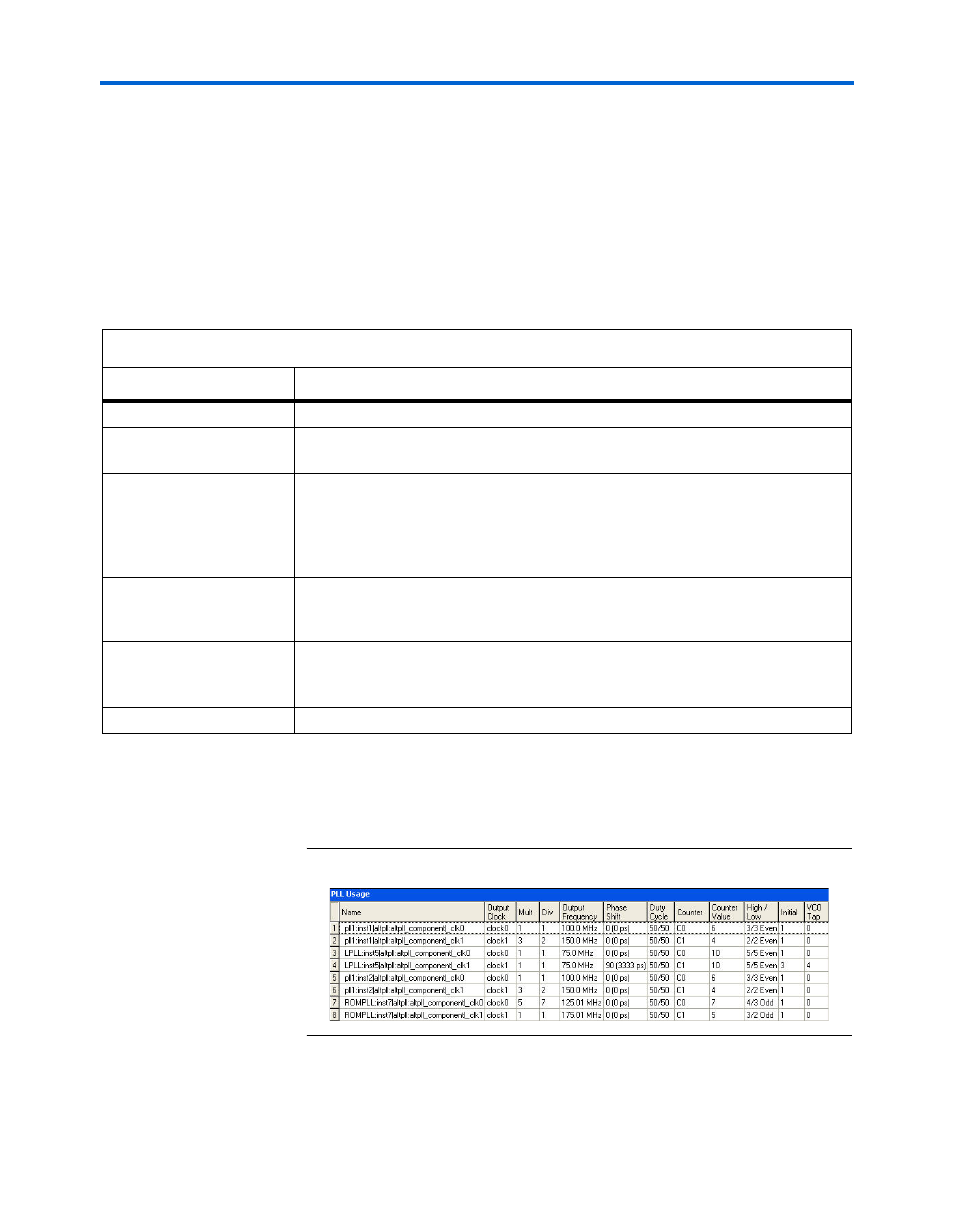

shows the PLL Usage section in the Quartus II software

Compilation Report for a design targeting a Cyclone II device. The

Compilation Report provides the maximum frequency a PLL outputs.

Figure 3–16. PLL Usage in Compilation Report

Table 3–7. PLL Section Information

Column Heading

Description

Module

Enter a name for the PLL in this column. This is an optional value.

# PLL Blocks

Enter the number of PLL blocks with the same specific output frequency and VCO

frequency combination.

Output Freq

Enter the maximum output frequency (f

MAX

) of the PLL in MHz. The maximum

output frequency is reported in the PLL Usage column of the Quartus II Compilation

Report under Fitter > Resource Section > PLL Usage > Output Frequency. If there

are multiple clock outputs from the PLL, choose the maximum output frequency

listed.

VCO Freq

Enter the frequency of the voltage controlled oscillator in MHz. The VCO frequency

is reported in the Nominal VCO frequency row of the Quartus II Compilation Report

under Fitter > Resource Section > PLL Summary > Nominal VCO frequency.

Total Power

This shows the estimated combined power for V

C C A

and V

C C D

in W, based on the

maximum output frequency and the VCO frequency you entered. This value is

calculated automatically.

User Comments

Enter any comments. This is an optional entry.