Altera Cyclone II PowerPlay Early Power Estimator User Manual

Page 24

3–8

Altera

Corporation

PowerPlay Early Power Estimator User Guide For Cyclone II FPGAs

May 2006

PowerPlay Early Power Estimator Spreadsheet Inputs

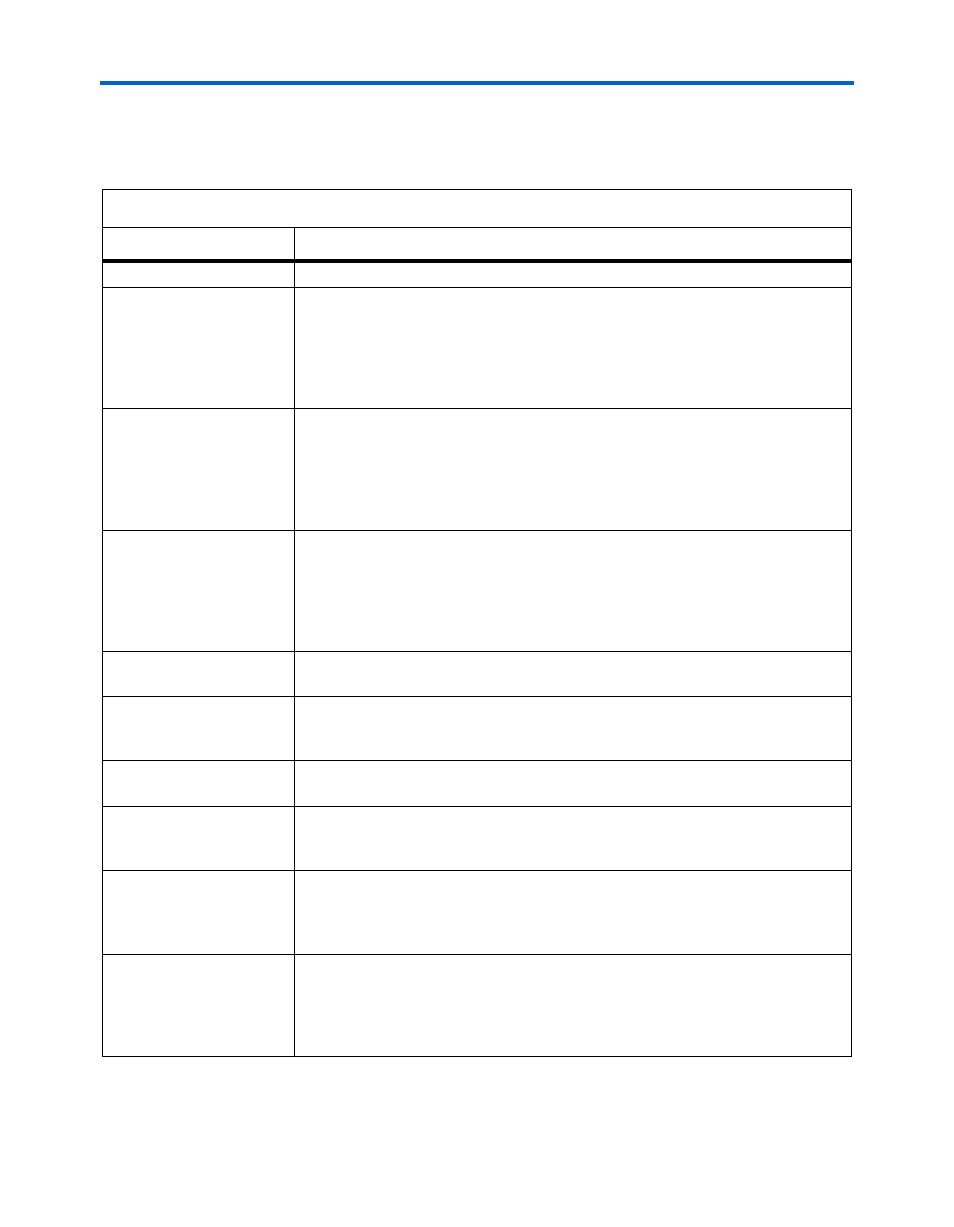

Table 3–3

describes the parameters in the RAM section of the PowerPlay

Early Power Estimator spreadsheet.

Table 3–3. RAM Section Information (Part 1 of 2)

Column Heading

Description

Module

Enter a name for the RAM module in this column. This is an optional value.

# RAM Blocks

Enter the number of RAM blocks in the module that have the same data width, RAM

mode, port parameters, and output toggle rate. The parameters for each port are:

clock frequency in MHz, the percentage of time the RAM clocks are enabled, and

the percentage of time the port is writing as opposed to reading. The number of

RAM blocks reported can be found in the M4K row of the Quartus II Compilation

Report under Fitter > Resource Section > Resource Usage Summary.

Data Width

Enter the width of the data for the RAM block. This value must be between 1 and

18 for RAM blocks in true dual-port mode. This value must be between 1 and 36 for

all other RAM modes. For RAM blocks that have different widths for port A and port

B, use the larger of the two widths. The width of the RAM block can be found in the

Port A Width or the Port B Width column of the Quartus II Compilation Report under

Fitter > Resource Section > RAM Summary.

RAM Mode

Select from the following modes: Single-Port, Simple Dual-Port, True Dual-Port,

ROM. The mode is based on how the Quartus II Compiler will implement the RAM.

If you are unsure how your memory module will be implemented it is best to compile

a test case in the required configuration in the Quartus II software. The RAM mode

can be found in the Mode column of the Quartus II Compilation Report under Fitter

> Resource Section > RAM Summary.

Port A – Clock Freq

Enter the clock frequency for port A of the RAM block(s) in MHz. This value is

limited by the maximum frequency specification for the RAM type and device family.

Port A – Enable %

Enter the average percentage of time the input clock enable for port A is active,

regardless of activity on RAM data and address inputs. The enable percentage

ranges from 0 to 100%. The default is set to 25%.

Port A – Write %

Enter the average percentage of time port A of the RAM block is in write mode

versus read mode. This is ignored for RAM blocks in ROM mode.

Port B – Clock Freq

Enter the clock frequency for port B of the RAM block(s) in MHz. This value is

limited by the maximum frequency specification for the RAM type and device family.

Port B is ignored for RAM blocks in ROM or single-port mode.

Port B – Enable %

Enter the average percentage of time the input clock enable for port B is active,

regardless of activity on RAM data and address inputs. The enable percentage

ranges from 0 to 100%. The default is set to 25%. Port B is ignored for RAM blocks

in ROM or single-port mode.

Port B – R/W %

For RAM blocks in true dual-port mode, enter the average percentage of time port

B of the RAM block is in write mode versus read mode. For RAM blocks in simple

dual-port mode, enter the percentage of time port B of the RAM block is reading.

You cannot write to port B in simple dual-port mode. Port B is ignored for RAM

blocks in ROM or single-port mode.