General i/o pins – Altera Cyclone II PowerPlay Early Power Estimator User Manual

Page 29

Altera Corporation

3–13

May 2006

PowerPlay Early Power Estimator User Guide For Cyclone II FPGAs

Using the Cyclone II PowerPlay Early Power Estimator

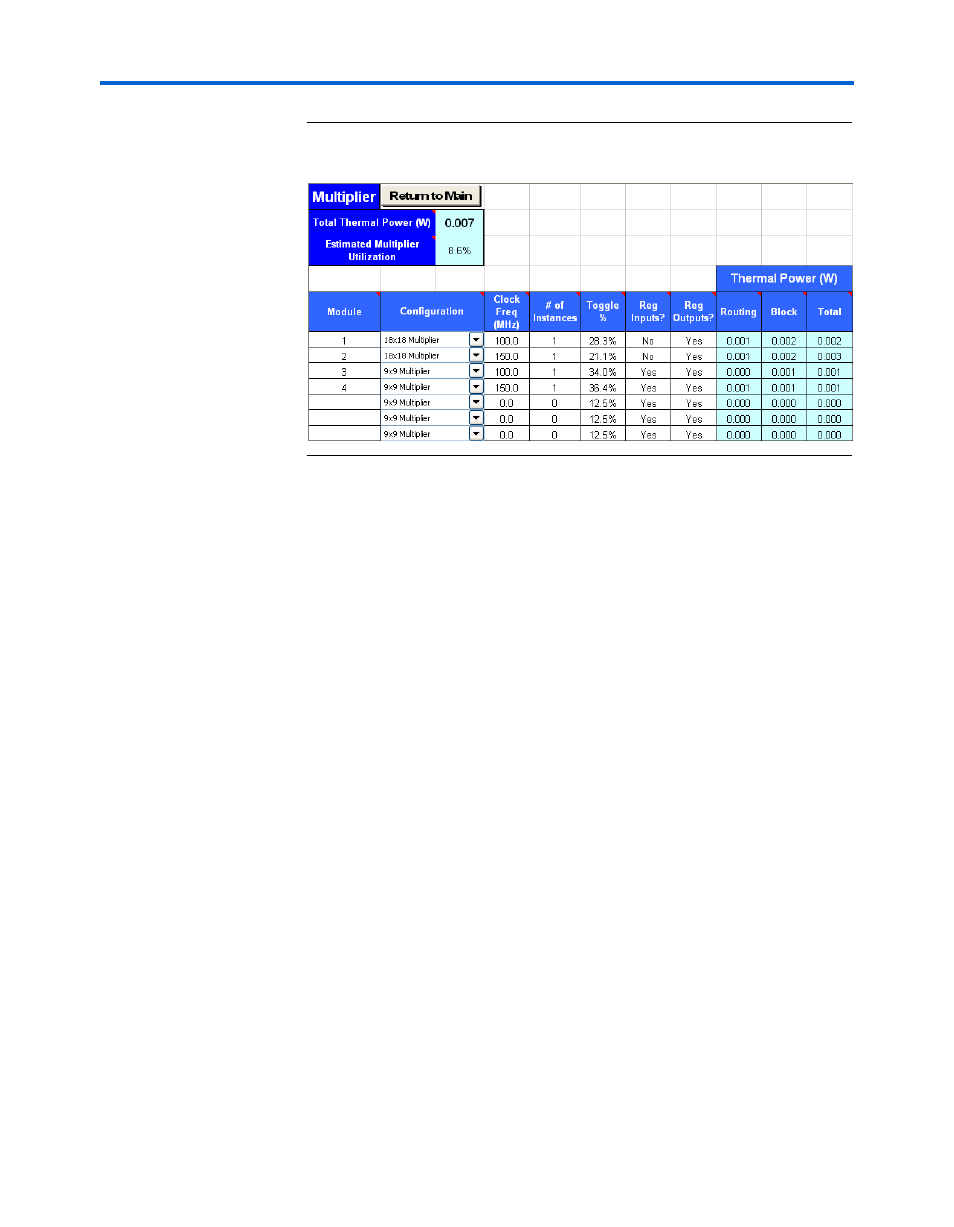

Figure 3–9. Multiplier Section in the PowerPlay Early Power Estimator

Spreadsheet

General I/O Pins

Cyclone II devices feature programmable I/O pins that support a wide

range of industry I/O standards for increased design flexibility. The I/O

section in the PowerPlay Early Power Estimator spreadsheet allows you

to estimate the I/O pin power consumption based on the pin’s I/O

standards.

1

The PowerPlay Early Power Estimator spreadsheet assumes you

are using external termination resistors when you design with

I/O standards that recommend termination resistors (e.g., SSTL

and HSTL). If your design does not use external termination

resistors, you should choose the LVTTL I/O standard with the

same V

CCIO

and similar drive strength as the terminated I/O

standard. For example, if you are using the SSTL-2 class II I/O

standard without termination resistors (using a point-to-point

connection), you should select LVTTL/LVCMOS 2.5-V as your

I/O standard and 16mA as the Drive Strength in the PowerPlay

Early Power Estimator spreadsheet.

The power reported for I/O signals includes thermal and external I/O

power. The total thermal power is the sum of the thermal power

consumed by the device based on each power rail.

thermal power = thermal P

INT

+ thermal P

IO

shows a graphical representation of the I/O power

consumption. The I

CCIO

rail power includes both the thermal P

IO

and the

external P

IO

.