Altera Cyclone II PowerPlay Early Power Estimator User Manual

Page 25

Altera Corporation

3–9

May 2006

PowerPlay Early Power Estimator User Guide For Cyclone II FPGAs

Using the Cyclone II PowerPlay Early Power Estimator

Figure 3–6

shows the Resource Usage Summary section in the Quartus II

software Compilation Report for a design targeting the Cyclone II device

family. The Compilation Report provides the number of RAM resources

being used.

Figure 3–7

shows the RAM Summary in the Quartus II

software Compilation Report for a design targeting the Cyclone II device

family. The Compilation Report provides the RAM mode and the data

width.

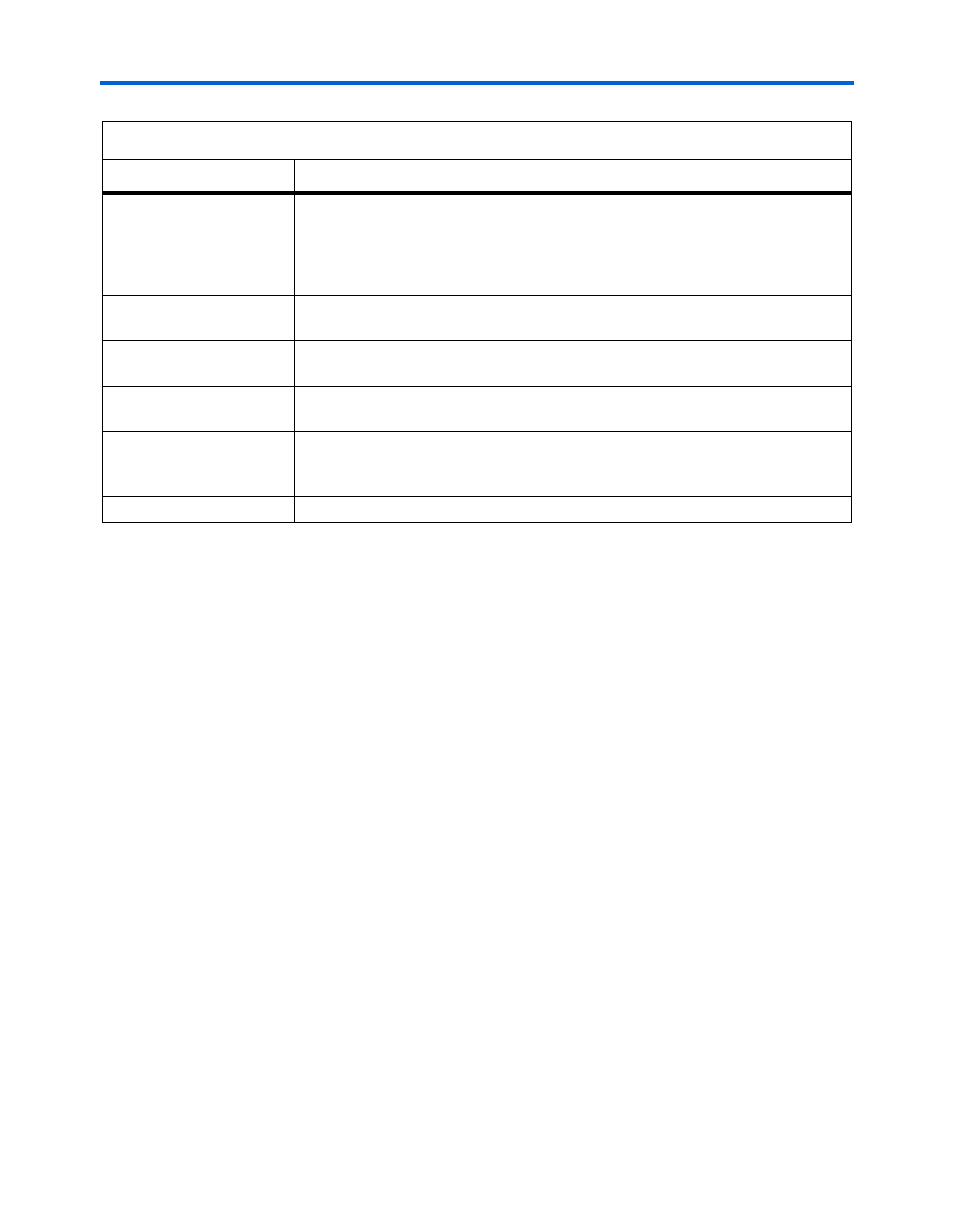

Toggle %

Average percentage of clock cycles that each block output signal changes value.

Multiplied by clock frequency to determine number of transitions per second.

50% corresponds to a randomly changing signal. A random signal changes states

only half the time.

Valid Width/Mode

This check will fail if the entered data width exceeds that allowed by the RAM mode.

See the description of the data width column for details.

Thermal Power (W),

Routing

This shows the estimated power consumed by the routing in W. This value is

calculated automatically.

Thermal Power (W), Block

This shows the estimated power consumed by the RAM blocks in W. This value is

calculated automatically.

Thermal Power (W), Total

This shows the estimated power in W, based on the inputs you entered. It is the total

power consumed by RAM blocks and is equal to the routing power and the block

power. This value is calculated automatically.

User Comments

Enter any comments. This is an optional entry.

Table 3–3. RAM Section Information (Part 2 of 2)

Column Heading

Description