Estimating power before starting the fpga design, Estimating power while creating the fpga design – Altera Cyclone II PowerPlay Early Power Estimator User Manual

Page 10

2–2

Altera

Corporation

PowerPlay Early Power Estimator User Guide For Cyclone II FPGAs

May 2006

Estimating Power

an existing design, then you need to estimate the number of device

resources your design will use in order to enter the information into the

PowerPlay Early Power Estimator spreadsheet.

Estimating Power Before Starting the FPGA Design

FPGAs provide the convenience of a shorter design cycle and faster time-

to-market than ASICs or ASSPs. This means that the board design often

takes places during the FPGA design cycle, and the power planning for

the device can happen before any of the FPGA design is complete.

Table 2–1

shows the advantages and disadvantages of using the

PowerPlay Early Power Estimator spreadsheet before you begin the

FPGA design.

To estimate power usage with the PowerPlay Early Power Estimator

spreadsheet if you have not started your FPGA design, perform the

following steps.

1.

Download the PowerPlay Early Power Estimator spreadsheet from

the Altera website (www.altera.com).

2.

Select the target device and package from the PowerPlay Early

Power Estimator spreadsheet’s Device section.

3.

Enter values in the fields on each section of the PowerPlay Early

Power Estimator spreadsheet. Different worksheets in the file

display different power sections, such as clocks and PLLs. Power is

calculated automatically, and subtotals are given for each section.

4.

The calculator displays the estimated power usage in the Total

section.

Estimating Power While Creating the FPGA Design

When the FPGA design is partially complete, you can use the power

estimation file (<revision name>_early_pwr.csv) generated by the

Quartus II software to supply information to the PowerPlay Early Power

Estimator spreadsheet. After importing the power estimation file

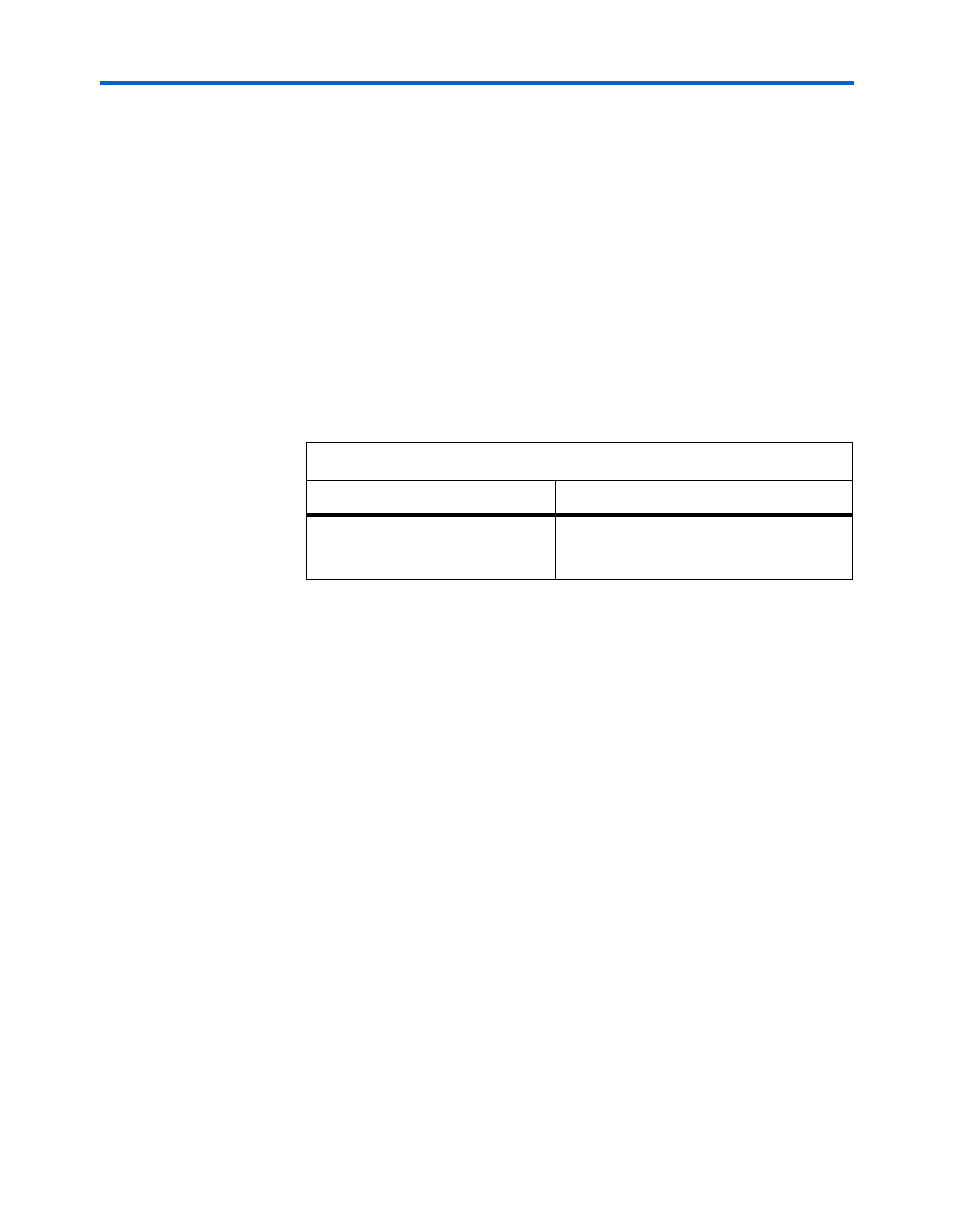

Table 2–1. Power Estimation Before Designing FPGA

Advantages

Disadvantages

Power estimation can be done

before any FPGA design is

complete

●

Accuracy depends on user input and

estimate of the device resources

●

Process can be time consuming