Altera Cyclone II PowerPlay Early Power Estimator User Manual

Page 32

3–16

Altera

Corporation

PowerPlay Early Power Estimator User Guide For Cyclone II FPGAs

May 2006

PowerPlay Early Power Estimator Spreadsheet Inputs

describes the parameters in the I/O section of the PowerPlay

Early Power Estimator spreadsheet.

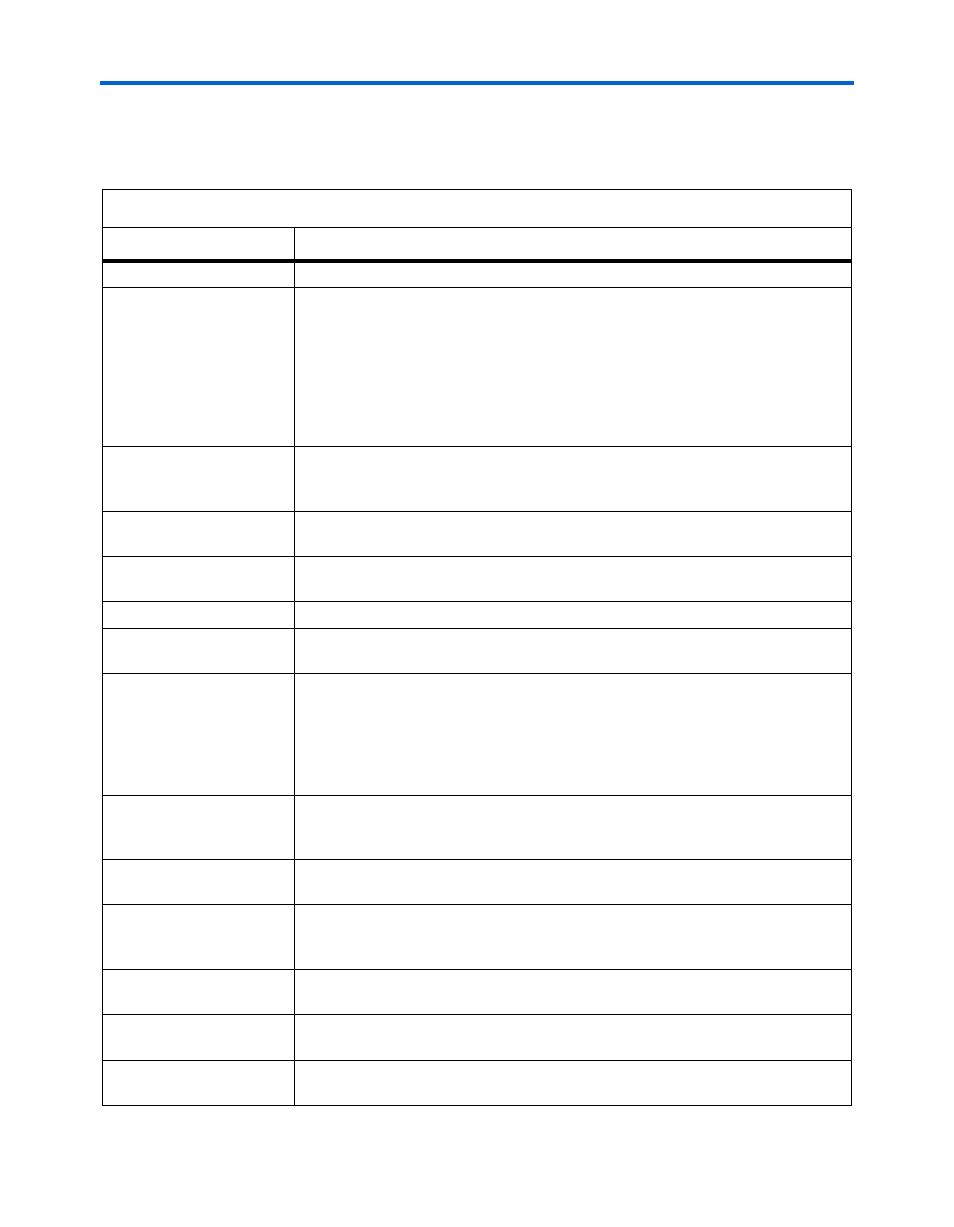

Table 3–6. I/O Section Information (Part 1 of 2)

Column Heading

Description

Module

Enter a name for the module in this column. This is an optional value.

I/O Standard

Select the I/O standard used for the input, output or bidirectional pins in this module

from the list. The calculated I/O power varies based on the I/O standard. For I/O

standards that recommend termination (SSTL and HSTL), the PowerPlay Early

Power Estimator spreadsheet assumes you are using external termination

resistors. If you are not using external termination resistors, you should choose the

LVTTL I/O standard with the same voltage and similar drive strength as the

terminated I/O standard. There are up and down scroll bars to view all the I/O

standards in the drop-down list.

Clock Freq

Enter the clock frequency for the module in MHz. This is the frequency of the clock

used to feed the I/O registers or the registers that feed the I/O pins. This value is

limited by the maximum I/O pin frequency specification for the device family.

# Output Pins

Enter the number of output pins used in this module. A differential pair of pins

should be considered as one pin.

# Input Pins

Enter the number of input pins used in this module. A differential pair of pins should

be considered as one pin.

# Bidir Pins

Enter the number of bidirectional pins used in this module.

I/O Bank

Select the I/O bank the module will be located in. If you do not know which I/O bank

the pins will be assigned to, leave the value as “?.”

Toggle %

Enter the average percentage of output and bidirectional pins toggling on each

clock cycle. The toggle percentage ranges from 0 to 200%. If the pin uses a double

data rate (DDR), you can set the data rate to single data rate (SDR) and double the

toggle percentage. The Quartus II software will often use this method to output

information. Typically the toggle percentage is 12.5%. To be more conservative,

you can use a higher toggle percentage.

OE %

Enter the average percentage of time that the output pin is enabled. This is only

applicable for bidirectional pins or in cases when output pins require an output

enable.

Load (pF)

Enter the average external capacitive load in pico-Farads (pF) for the output and

bidirectional pins in this clock domain.

Data Rate

Select either SDR or DDR as the I/O data rate. If the data rate of the pin is DDR, it

is possible to set the data rate to SDR and double the toggle percentage. The

Quartus II software will often use this method to output information.

Bank I/O Std Check

This indicates whether the selected I/O standard is available on the selected I/O

bank. Not all I/O banks can implement every I/O standard.

Bank Voltage Check

This indicates whether or not the selected I/O bank has a voltage compatible with

the selected I/O standard.

Thermal Power (W),

Routing

This shows the estimated I/O power consumed by the routing in W. This value is

calculated automatically.