Altera Parallel Flash Loader IP User Manual

Page 3

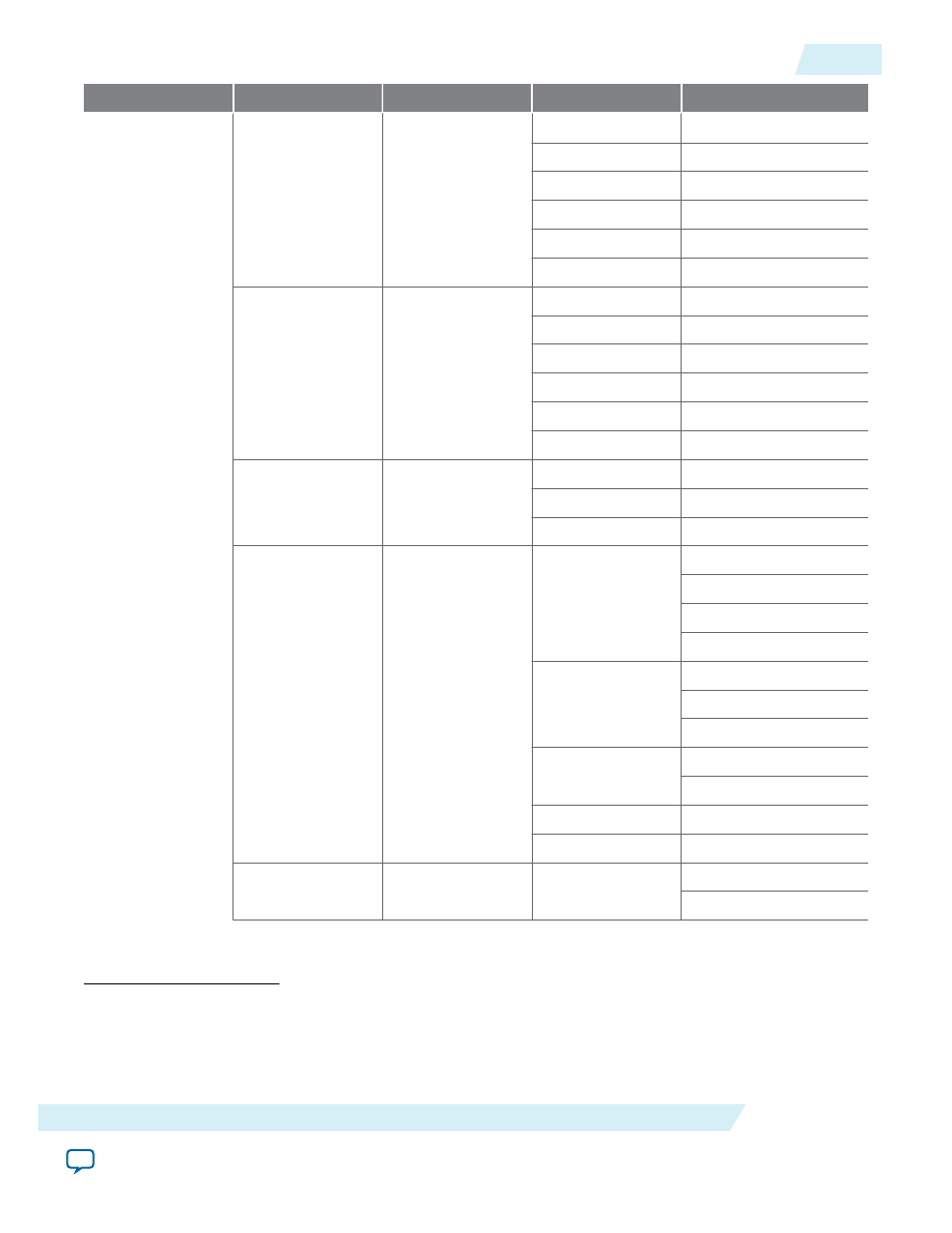

Manufacturer

Product Family

Data Width

Density (Megabit)

Device Name

(1)(2)

P30

16

64

28F640P30

128

28F128P30

256

28F256P30

512

28F512P30

1000

28F00AP30

2000

28F00BP30

P33

16

128

28F128P33

256

28F256P33

512

28F512P33

640

28F640P33

1000

28F00AP33

2000

28F00BP33

M29EW

8 or 16

256

28F256M29EW

512

28F512M29EW

1000

28F00AM29EW

M29W

8 or 16

16

M28W160CT

M28W160CB

M29W160F7

M29W160FB

32

M29W320E

M29W320FT

M29W320FB

64

M29W640F

M29W640G

128

M29W128G

256

M29W256G

M29DW

8 or 16

32

M29DW323DT

M29DW323DB

(1)

Spansion has discontinued the Spansion S29GL-N flash memory device family. Altera does not recommend

using this flash memory device. For more information about an alternative recommendation, see related

information.

(2)

The PFL IP core supports top and bottom boot block of the flash memory devices. For Micron flash memory

devices, the PFL IP core supports top, bottom, and symmetrical blocks of flash memory devices.

UG-01082

2015.01.23

Supported Flash Memory Devices

3

Parallel Flash Loader IP Core User Guide

Altera Corporation

- MAX 10 JTAG (15 pages)

- MAX 10 Power (21 pages)

- Unique Chip ID (12 pages)

- Remote Update IP Core (43 pages)

- Device-Specific Power Delivery Network (28 pages)

- Device-Specific Power Delivery Network (32 pages)

- Hybrid Memory Cube Controller (69 pages)

- ALTDQ_DQS IP (117 pages)

- MAX 10 Embedded Memory (71 pages)

- MAX 10 Embedded Multipliers (37 pages)

- MAX 10 Clocking and PLL (86 pages)

- MAX 10 FPGA (26 pages)

- MAX 10 FPGA (56 pages)

- USB-Blaster II (22 pages)

- GPIO (22 pages)

- LVDS SERDES (27 pages)

- User Flash Memory (33 pages)

- ALTDQ_DQS2 (100 pages)

- Avalon Tri-State Conduit Components (18 pages)

- Cyclone V Avalon-MM (166 pages)

- Cyclone III FPGA Starter Kit (36 pages)

- Cyclone V Avalon-ST (248 pages)

- Stratix V Avalon-ST (286 pages)

- Stratix V Avalon-ST (293 pages)

- DDR3 SDRAM High-Performance Controller and ALTMEMPHY IP (10 pages)

- Arria 10 Avalon-ST (275 pages)

- Avalon Verification IP Suite (224 pages)

- Avalon Verification IP Suite (178 pages)

- FFT MegaCore Function (50 pages)

- DDR2 SDRAM High-Performance Controllers and ALTMEMPHY IP (140 pages)

- Floating-Point (157 pages)

- Integer Arithmetic IP (157 pages)

- Embedded Peripherals IP (336 pages)

- JESD204B IP (158 pages)

- Low Latency Ethernet 10G MAC (109 pages)

- LVDS SERDES Transmitter / Receiver (72 pages)

- Nios II Embedded Evaluation Kit Cyclone III Edition (3 pages)

- Nios II Embedded Evaluation Kit Cyclone III Edition (80 pages)

- IP Compiler for PCI Express (372 pages)

- Nios II C2H Compiler (138 pages)

- RAM-Based Shift Register (26 pages)

- RAM Initializer (36 pages)

- Phase-Locked Loop Reconfiguration IP Core (51 pages)

- DCFIFO (28 pages)