Altera Parallel Flash Loader IP User Manual

Page 21

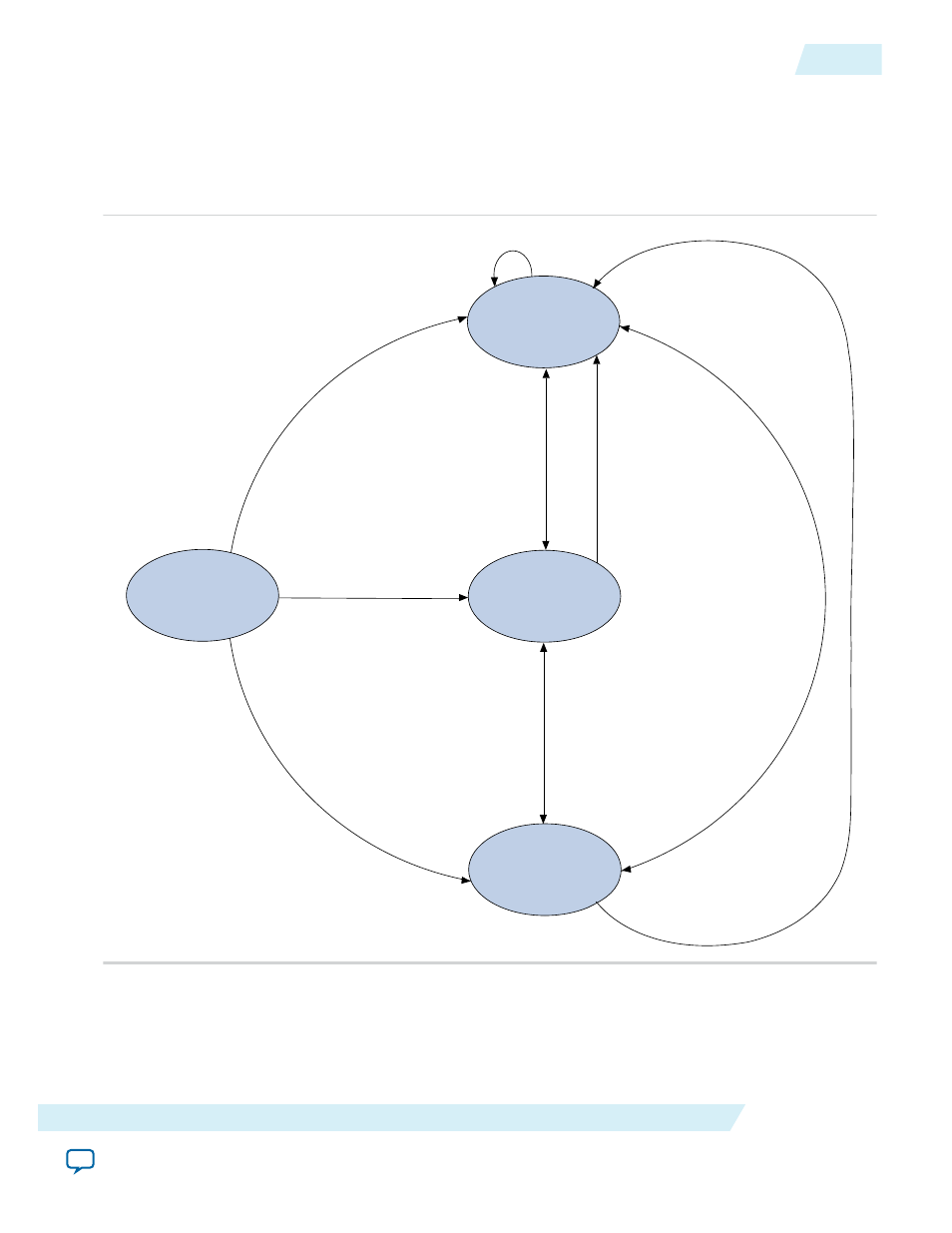

Figure 18: Transitions Between Different Configurations in Remote System Upgrade

• The remote system upgrade feature in the PFL IP core does not restrict the factory image to page 0, but

allows the factory image to be located on other pages in the flash.

• You can load the FPGA with either a factory image or any application image after power up,

depending on the

fpga_pgm[2..0]

setting.

Application 1

Configuration

Power-up

Factory

Configuration

Application n

Configuration

fpga_pgm[2..0] is set to

factory page

Set fpga_pgm[2..0] to

intended page and pulse

pfl_nreconfig

fpga_pgm[2..0] is set to

application 1 page

Configuration Error

Configuration Error

Configuration Error

fpga_pgm[2..0] is set to

application n page

Set fpga_pgm[2..0] to

intended page and pulse

pfl_nreconfig

Set fpga_pgm[2..0] to

intended page and pulse

pfl_nreconfig

Note: The PFL IP core can implement a Last Revision First programming order. The application image is

updated with remote system upgrade capabilities. If a flash programming error causes the FPGA

configuration to fail, the FPGA is reconfigured from the factory image address. A system shipped

from the factory has the same configuration file at the application image address and the factory

UG-01082

2015.01.23

Remote System Upgrade State Machine in the PFL IP Core

21

Parallel Flash Loader IP Core User Guide

Altera Corporation