Booting image redundancy, Lmp u-boot redundancy – ADLINK aTCA-N700 User Manual

Page 25

aTCA-N700 SW Users Guide

19

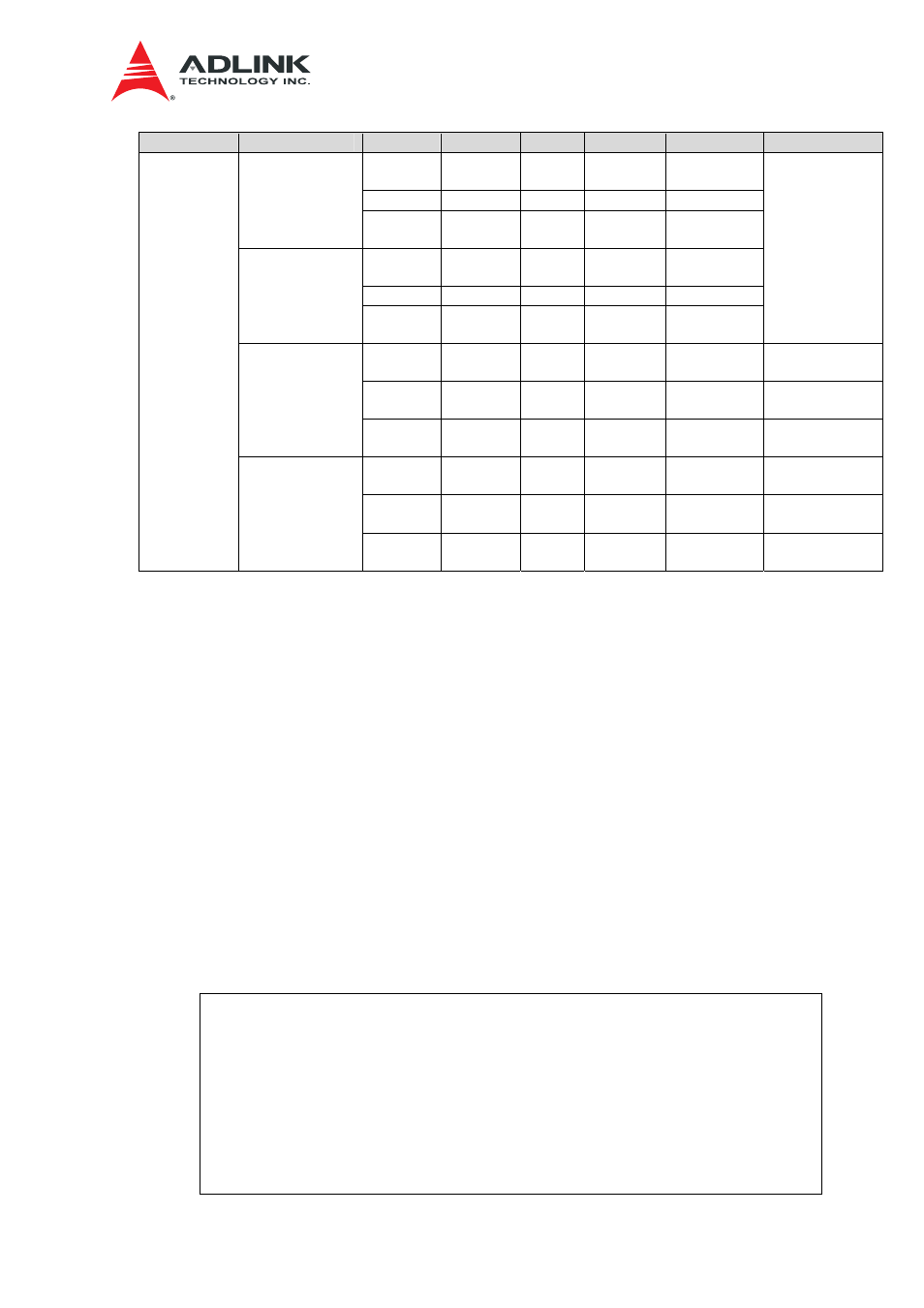

Host

Device

Size

Contents format U-Boot

linux

Remark

1MiB

U-Boot

image

binary read/write

/dev/mtd0

6MiB Reserved

binary

read/write

/dev/mtd1

NOR_FLASH1

1MiB

U-Boot

Env.

binary read/write

/dev/mtd2

1MiB

U-Boot

image

binary read/write

/dev/mtd0

6MiB Reserved

binary

read/write

/dev/mtd1

NOR_FLASH2

1MiB

U-Boot

Env.

binary read/write

/dev/mtd2

Same S/W

access point to

NOR_FLASH1,

NOR_FLASH2.

Selected by a

CPLD register

256 MiB

OS

images

UBIFS read

only

/dev/ubi0

(/bootA)

256 MiB

System

config

UBIFS

no

access

/dev/ubi1

(/var/NVMA)

NAND_FLASH1

(remains)

user

defined

user

defined

no

access

-

256 MiB

OS

images

UBIFS read

only

/dev/ubi2

(/bootB)

256 MiB

System

config

UBIFS

no

access

/dev/ubi3

(/var/NVMB)

OCTEON_L

NAND_FLASH2

(remains)

user

defined

user

defined

no

access

-

5.1. Booting Image Redundancy

The aTCA-N700 S/W package provides booting image redundancy to survive a single

point of failure during a booting process. When a device with a CPU core boots up from

an image stored in a storage device, the system guarantees to boot up fine by having

redundant bootable images stored separately in a primary and a redundant storage

devices. The bootloader U-Boot image and the Linux operating system image are

stored in different storage devices.

The booting image redundancy applies to both the LMP and the dual Octeons as

summarized below.

• LMP U-Boot image redundancy

• LMP OS image redundancy

• NP U-Boot image redundancy

• NP OS image redundancy

5.1.1. LMP U-Boot Redundancy

The U-Boot image is stored in a SPI flash memory. On the aTCA-N700, the LMP has

two of such U-Boot flash memories in a primary and a redundant fashion.

To select one of the redundant images, use the following example.

=>

ipmi active-flash

-> shows current active flash (result = 0 or 1)

active-flash: 0 -> means active-flash is the first one.

=>

ipmi switch-active

-> change active flash to the second one (toggle

fashion).

-> A reset occurs automatically.

U-Boot 2011.09-svn118 (Jul 08 2013 - 19:25:54)

CPU0: P2041E, Version: 1.1, (0x82180111)

Core: E500MC, Version: 2.2, (0x80230022)

Clock Configuration: