Output data file, Over-range flag bits (o0…o15), Under-range flag bits (u0…u15) – Rockwell Automation 1769-IF16V Compact High Density Analog Input Modules User Manual

Page 33

Publication 1769-UM018A-EN-P - October 2008

33

Module Data, Status, and Channel Configuration Chapter 3

Over-Range Flag Bits (O0…O15)

Over-range bits for channels 0…15 are contained in Words 18…21,

bits 0, 4, 8, and 12. When set (1), this bit indicates an input signal is

beyond the normal operating range. For the 1769-IF16V module, it

may also indicate an open circuit condition. However, the module

continues to convert analog data to the maximum full range value.

The bit is automatically reset (0) by the module when the over-range

condition is cleared and the data value is within the normal operating

range.

Under-Range Flag Bits (U0…U15)

Under-range bits for channels 0…15 are contained in Words 18…21,

bits 1, 5, 9, and 13. When set (1), this bit indicates an input signal is

below the normal operating range. For the 1769-IF16C module, it may

also indicate an open circuit condition. However, the module

continues to convert analog data to the minimum full range value. The

bit is automatically reset (0) by the module when the under-range

condition is cleared and the data value is within the normal operating

range.

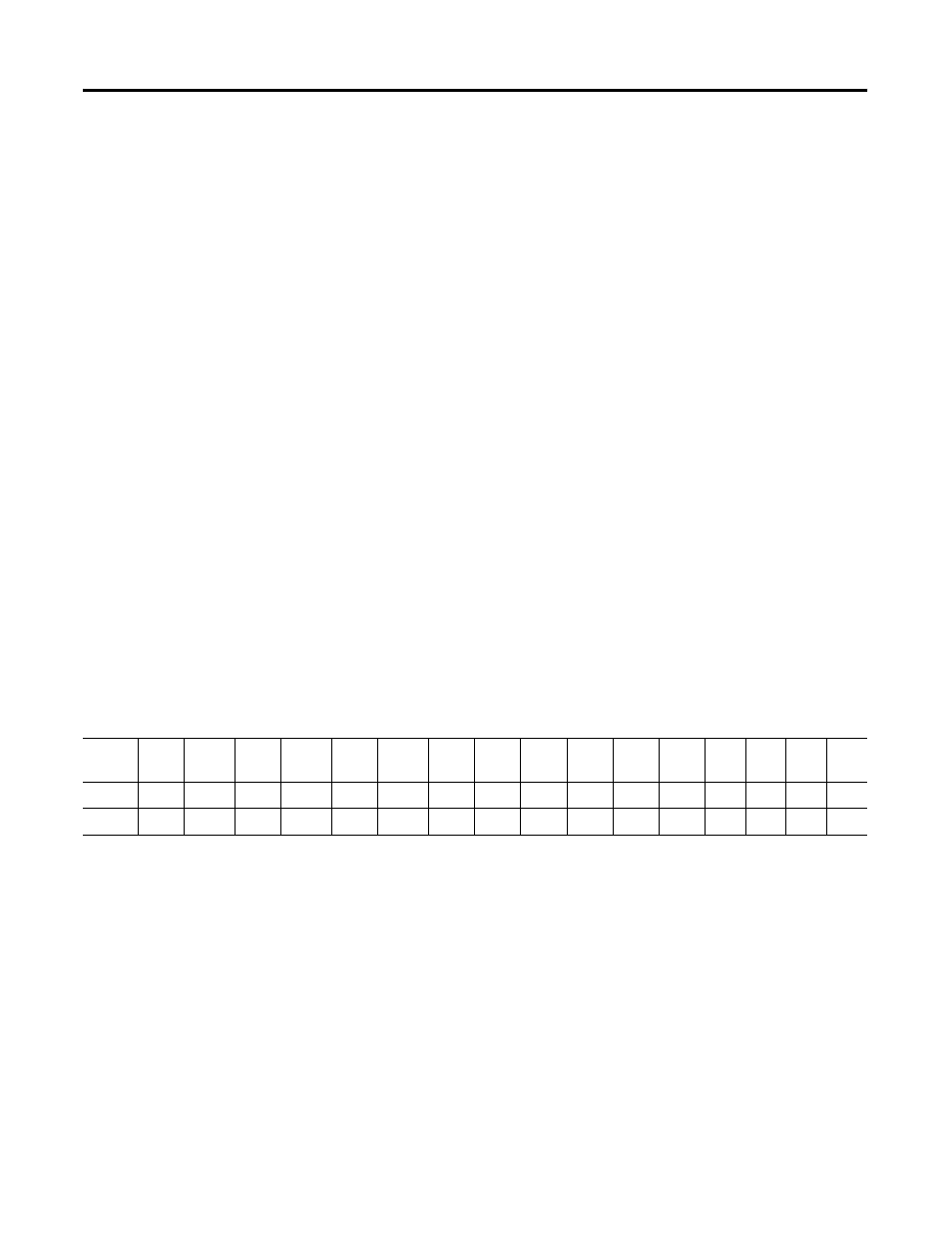

Output Data File

The output data table lets you access analog output module write data

for use in the control program, via word and bit access.

These bits are written during run mode to cancel any latched low- and

high-process alarms. The alarm is unlatched when the unlatch bit is

set (1) and the alarm condition no longer exists. If the alarm condition

persists, then the unlatch bit has no effect until the alarm condition no

longer exists. You need to keep the unlatch bit set until verification

from the appropriate input channel status word that the alarm status

bit has cleared (0). Then you need to reset (0) the unlatch bit. The

module will not latch an alarm condition if a transition from ‘no alarm’

to ‘alarm’ occurs while a channel’s cancel latch bit is set.

Word/

Bit

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

Word 0 CLL7

CLH7

CLL6

CLH6

CLL5

CLH5

CLL4

CLH4

CLL3

CLH3

CLL2

CLH2

CLL1 CLH1 CLL0 CLH0

Word 1 CLL15 CLH15

CLL14 CLH14

CLL13 CLH13

CLL12 CLH12 CLL11 CLH11 CLL10 CLH10 CLL9 CLH9 CLL8 CLH8