Switching specifications: adsp in i, Cs35l32 – Cirrus Logic CS35L32 User Manual

Page 13

DS963F4

13

CS35L32

3 Characteristics and Specifications

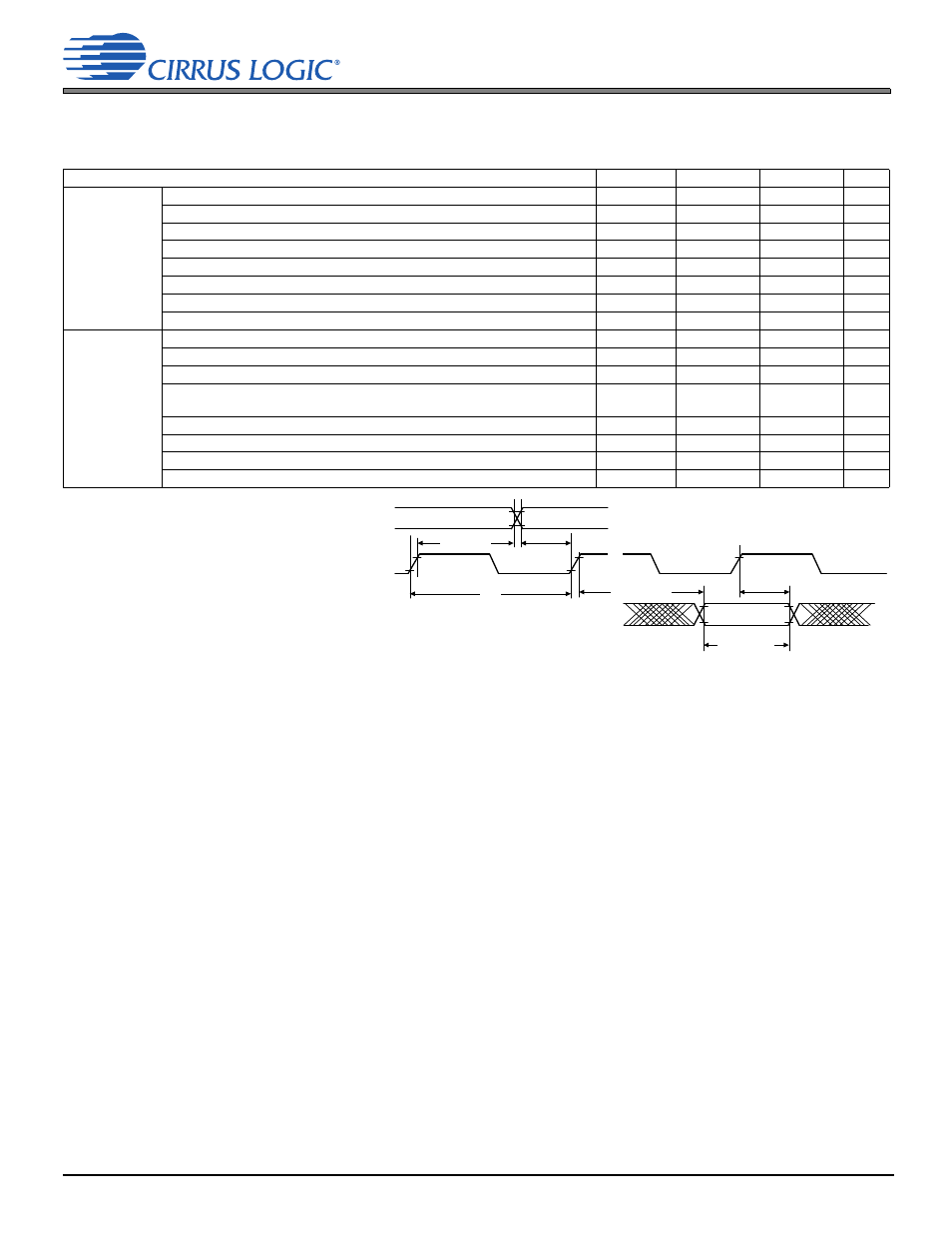

Table 3-12. Switching Specifications: ADSP in I

2

S Mode

Test conditions, except where noted otherwise: VA = 1.8 V, VP = 3.6 V, VBST = 5.0 V, T

A

= +25°C, Inputs: Logic 0 = GNDA = GNDP = 0 V, Logic 1 =

VA; C

LOAD

= 30 pF.

describes some parameters in detail; input timings are measured at V

IL

and V

IH

thresholds; output timings are measured

at V

OL

and V

OH

thresholds (see

Parameters

Symbol

1

1.ADSP timing in I

2

S Mode

Min Max

Units

Slave Mode

Input sample rate (LRCK)

2

2.Clock rates should be stable when the CS35L32 is powered up.

Fs

—

49

kHz

LRCK duty cycle

—

45

55

%

SCLK frequency

1/t

Ps

—

64•Fs

Hz

SCLK duty cycle

—

45

55

%

LRCK setup time before SCLK rising edge

t

SS(LK–SK)

40

—

ns

LRCK hold time after SCLK rising edge

t

HS(SK–LK)

20

—

ns

SDOUT time from SCLK to data valid start

3

3.Minimum data valid window, as shown in signal diagram, is (SCLKperiod – 300 + 155) ns. For SCLK = 64*Fs =64*48 = 3072 kHz, this is 180 ns.

t

DataValidStrt

—

300

ns

SDOUT time from SCLK to data valid end

t

DataValidEnd

155

—

ns

Master Mode

OUTPUT sample rate (LRCK)

4

4.In Master Mode, the output sample rate follows MCLK rate divided down per

. Any deviation in internal MCLK from the

nominal supported rates is directly imparted to the output sample rate by the same factor (e.g., +100-ppm offset in the frequency of MCLK becomes

a +100-ppm offset in LRCK).

Fs

—

[4]

kHz

LRCK duty cycle

—

45

55

%

SCLK frequency

1/t

PM

—

64•Fs

Hz

SCLK duty cycle

RATIO = 0

RATIO = 1

[5]

5.If RATIO = 1, the MCLK(INT)-to-LRCK ratio is 125. The device periodically extends SCLK high time to compensate for a fractional MCLK/SCLK ratio

—

—

45

33

55

67

%

%

LRCK setup time before SCLK rising edge

t

SM(LK–SK)

35

—

ns

LRCK hold time after SCLK rising edge

t

HM(SK–LK)

20

—

ns

SDOUT time from SCLK to data valid start

t

DataValidStrt

—

300

ns

SDOUT time from SCLK to data valid end

t

DataValidEnd

155

—

ns

//

LRCK

SCLK

SDOUT

T

P

Note:

= “S” or “M”

t

S

(LK-SK)

t

H

(SK-LK)

t

DataValidStrt

t

DataValidEnd

DataValidWind