Rainbow Electronics DS2172 User Manual

Page 12

DS2172

031197 12/20

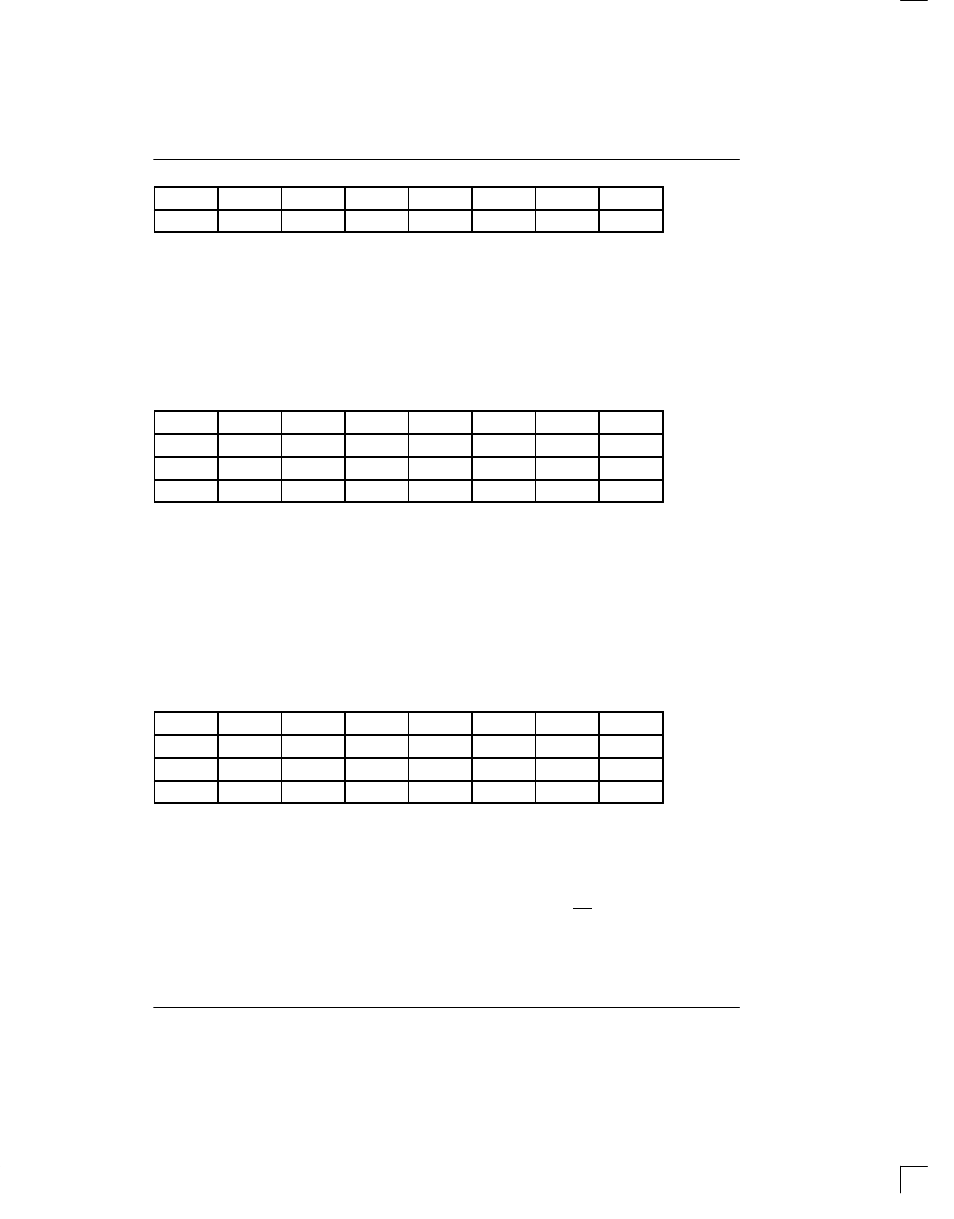

BC15

BC14

BC13

BC12

BC11

BC10

BC9

BC8

BC7

BC6

BC5

BC4

BC3

BC2

BC1

BC0

9.0 BIT ERROR COUNT REGISTERS

The Bit Error Count Registers (BECR3 to BECR0) com-

prise a 32–bit count of bits received in error at RDATA.

The bit error counter is disabled during loss of SYNC.

BEC31 is the MSB of the 32 bit count. The Status Regis-

ter bit BECOF is set when this 32–bit register overflows.

Upon an overflow condition, the user must clear the

BECR by either toggling the LC bit or pin. The DS2172

latches the bit error count into the BECR registers and

clears the internal bit error count when either the PCR.4

bit or the LC input pin toggles from low to high. The bit

count (available via the BCRs) and bit error count are

used by an external processor to compute the BER per-

formance on a loop or channel basis.

BIT ERROR COUNT REGISTERS

(MSB)

(LSB)

BEC31

BEC30

BEC29

BEC28

BEC27

BEC26

BEC25

BEC24

BEC23

BEC22

BEC21

BEC20

BEC19

BEC18

BEC17

BEC16

BEC15

BEC14

BEC13

BEC12

BEC11

BEC10

BEC9

BEC8

BEC7

BEC6

BEC5

BEC4

BEC3

BEC2

BEC1

BEC0

10.0 PATTERN RECEIVE REGISTERS

The Pattern Receive Register (PRR) provide access to

the data patterns received at RDATA. The operation of

these registers depends on the synchronization status

of the DS2172. Asserting the RL bit (PCR.3) or pin dur-

ing an out–of –sync condition (SR.0 = 0) will latch the

previous 32 bits of data received at RDATA into the PRR

registers. When the DS2172 is in sync (SR.0 = 1)

asserting RL will latch the pattern that to which the

device has established synchronization. Since the

receiver has no knowledge of the start or end of the pat-

tern, the data in the PRR registers will have no particular

alignment. As an example, if the receiver has synchro-

nized to the pattern 00100110, PRR1 may report

10011000, 11000100 or any rotation thereof. Once syn-

chronization is established, bit errors cannot be viewed

in the PRR registers.

PATTERN RECEIVE REGISTERS

(MSB)

(LSB)

PR31

PR30

PR29

PR28

PR27

PR26

PR25

PR24

PR23

PR22

PR21

PR20

PR19

PR18

PR17

PR16

PR15

PR14

PR13

PR12

PR11

PR10

PR9

PR8

PR7

PR6

PR5

PR4

PR3

PR2

PR1

PR0

11.0 STATUS REGISTER AND INTERRUPT

MASK REGISTER

The Status Register (SR) contains information on the

current real time status of the DS2172. When a particu-

lar event has occurred, the appropriate bit in the register

will be set to a one. All of the bits in these registers

(except for the SYNC bit) operate in a latched fashion.

This means that if an event occurs and a bit is set to a

one in any of the registers, it will remain set until the user

reads that bit. For the BED, BCOF, and BECOF status

bits, they will be cleared when read and will not be set

again until the event has occurred again. For RLOS,

RA0, and RA1 status bits, they will be cleared when

read if the condition no longer persists.

The SR register has the unique ability to initiate a hard-

ware interrupt via the INT pin. Each of the alarms and

events in the SR can be either masked or unmasked

from the interrupt pins via the Interrupt Mask Register

(IMR).

BECR3

BECR2

BECR1

BECR0

(addr.=0C Hex)

(addr.=0D Hex)

(addr.=0E Hex)

(addr.=0F Hex)

PRR3

PRR2

PRR1

PRR0

(addr.=10 Hex)

(addr.=11 Hex)

(addr.=12 Hex)

(addr.=13 Hex)