Max9489 multiple-output network clock generator, Table 1. device i, C address selection – Rainbow Electronics MAX9489 User Manual

Page 8

MAX9489

Multiple-Output Network Clock Generator

8

_______________________________________________________________________________________

Writing to the MAX9489

Writing to the MAX9489 begins with a START condition

(Figures 3 and 4). Following the START condition, each

pulse on SCL transfers 1 bit of data. The first 7 bits

comprise the device address (see the Device Address

section). The 8th bit is low to indicate a write operation.

An acknowledge bit is then generated by the

MAX9489, signaling that it recognizes its address. The

next 8 bits form the register address byte (Table 2) and

determine which control register will receive the follow-

ing data byte. The MAX9489 then generates another

acknowledge bit. The data byte is then written into the

addressed register of the MAX9489. An acknowledge

bit by the MAX9489 followed by a required STOP con-

dition by the master complete the communication. To

write to the device again, repeat the entire write proce-

dure; I

2

C burst write mode is not supported by the

MAX9489.

Reading the MAX9489 Setup

Reading from the MAX9489 registers begins with a

START condition and a device address with the write

bit set low, then the register address that is to be read,

followed by a repeated START condition and a device

address with the write bit set high, and finally the data

are shifted out (Figure 4). Following a START condition,

the first 7 bits comprise the device address. The 8th bit

is low to indicate a write operation (to write in the

following register address). An acknowledge bit is

then generated by the MAX9489, signaling that it re-

cognizes its address. The next 8 bits form the register

address, indicating the location of the data to be read,

followed by another acknowledge, again generated by

the MAX9489. The master then produces a repeated

START condition and readdresses the device, this time

with the R/W bit high to indicate a read operation

(Figure 4). The MAX9489 generates an acknowledge

bit, signaling that it recognizes its address. The data

byte is then clocked out of the MAX9489. A final not-

acknowledge bit, generated by the master (not

required), and a STOP condition, also generated by the

master, complete the communication. To read from the

device again, the entire read procedure is repeated;

I

2

C burst read mode is not supported by the MAX9489.

Device Control Registers

The MAX9489 has 17 control registers. The register

addresses and functions are shown in Table 2. The first

16 registers are used to set the 15 outputs, with register

0x00 controlling all outputs simultaneously and the rest

mapped to individual outputs. Register 0x10 accesses

the frequency-margin control. All other addresses are

reserved and are not to be used.

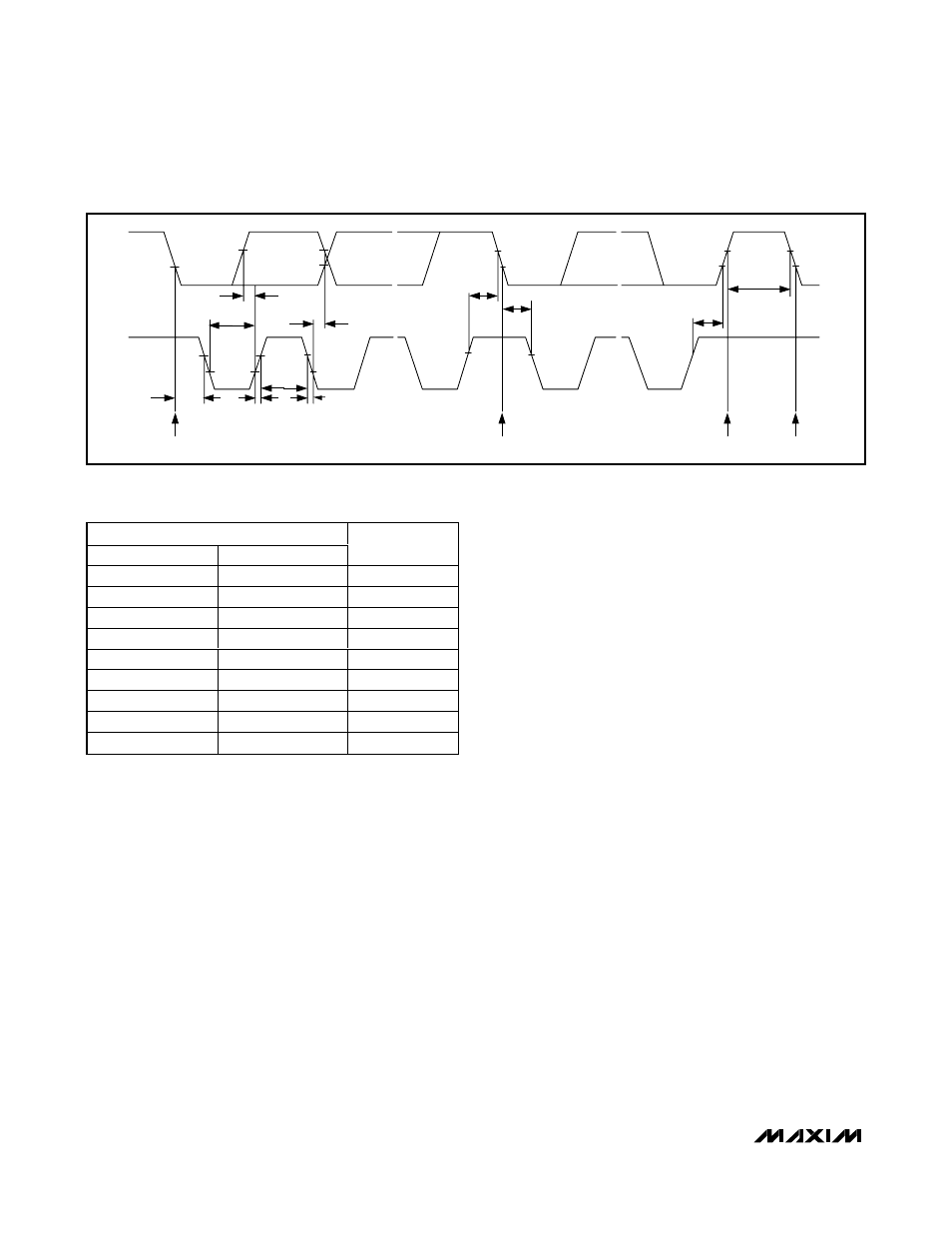

SCL

SDA

START CONDITION

STOP CONDITION

REPEATED START CONDITION

START CONDITION

t

SU, DAT

t

HD, DAT

t

LOW

t

HD, STA

t

HIGH

t

R

t

F

t

SU, STA

t

HD, STA

t

SU, STO

t

BUF

Figure 2. Serial Interface Timing

PIN

SA1

SA0

DEVICE

ADDRESS

Open

V

DD

110 0010

Open

GND

110 0100

Open

Open

110 1000

GND

V

DD

111 0000

GND

GND

110 1001

GND

Open

110 1100

V

DD

V

DD

111 0100

V

DD

GND

111 0010

V

DD

Open

111 0001

Table 1. Device I

2

C Address Selection